## Video Rate JPEG KL5A71007 datasheet

revision 1.4

| revision history |         |                       |

|------------------|---------|-----------------------|

| rev 0.1          | 97.1.27 | First Draft           |

| rev 0.2          | 97.3.13 | Register re-defined.  |

|                  |         | 80pin pitch changed.  |

| rev 0.2 a        | 97.6.25 | AC-timing added       |

| rev 0.3          | 97.9.22 |                       |

| rev 1.0          | 98.4.24 | Characteristics fixed |

| rev 1.1          | 98.9.10 | IDDS re-defined       |

| rev 1.2          | 99.1.19 | add max data reg      |

| rev 1.3          | 99.7.22 | add DHT notice        |

| rev 1.4          | 99.12.2 | FBGA80 canceled       |

## Kawasaki Steel Corporation

## LSI division

## 0)Contents

Chapter

- 1) Introduction -- Product feature

- 2) Specification overview

- 3) Chip Functionality

- 4) 80pin LQFP Pin Layout

- 5) Signal Descriptions

- 6) Registers

- 7) Control and data process flow

- 8) Electrical specifications DC Characteristics

- 9) Electrical specifications AC Characteristics

- 10) Typical System Configurations

- 11) spec difference from KL5A71006

- 12) 64pin LQFP Package usage guide

- 12.1) Functionality restriction

12.2) Pin Layout

- 12.3) Signal Description

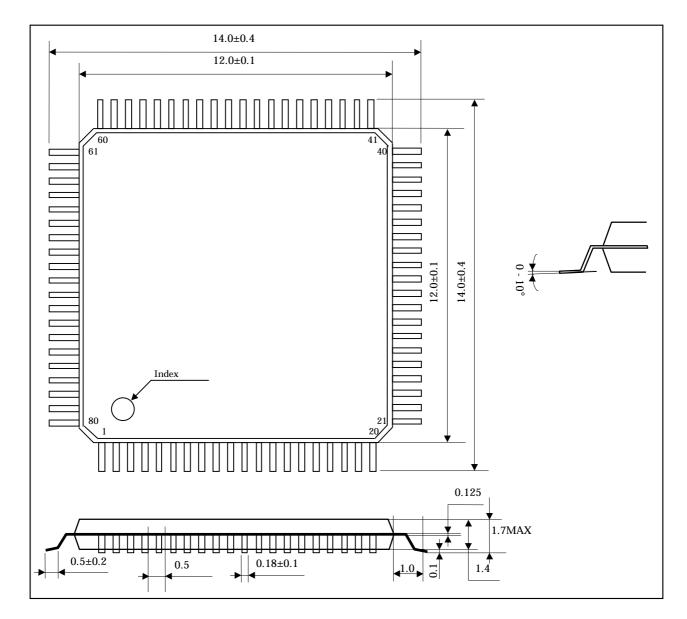

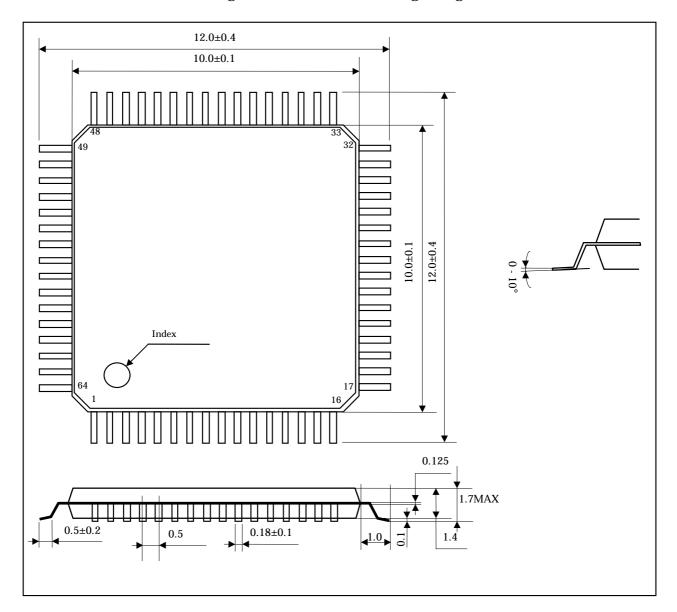

- 13) Package Specification

- 14) Known Bug list

- 15) Glossary

- 16) Index -- terms in alphabetical order

1)Introduction -- Product feature

KL5A71007 LSI is Kawasaki LSI's one chip JPEG hardware solution, which is enhanced its performance while maintaining the ease-of-use chip interface its precedence KL5A71006A has. This new chip has 8 times faster in operation than the previous chip.

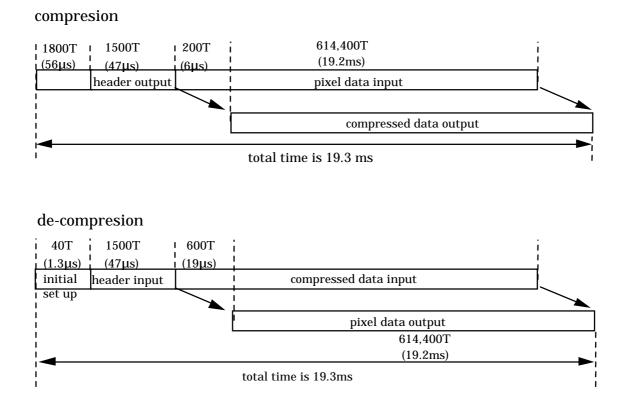

KL5A71007 can process either JPEG baseline compression or decompression by user setting. Although chip throughput deeply depends on the system configuration, Kawasaki set the chip design goal as follows.

- Optimized peak image processing throughput is 32Mbytes/sec.

For YUV 4:2:2 sampling color space data, VGA size (640 pixel by 480 line) one frame data is compressed or decompressed in around 20.5 milli-second by KL5A71007. For SXGA image (1,280 pixel by 1,024 line), this chip can produce to or reproduced by the compressed data in around 83 ms.

Both quantization table (Q-Table) and Huffman table (H-Table) are stored in on-chip RAMs. User can easily build up the table with writing table data, whose data entry sequence is very similar to that of JPEG DQT and DHT marker format.

KL5A71007 can produce to or re-produce image from the compressed data, which complies ISO/IEC 10918-1 JPEG standard baseline process.

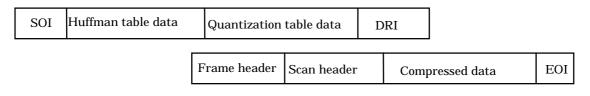

In addition to produce the bit stream data, KL5A71007 can handle JPEG header information, RST marker generation/decode by itself.

KL5A71007 has several data transfer modes, which expands the flexibility of system configuration.

------For VGA processing time VGA image data volume = (640 x 480)pixel/frame x 2bytes/pixel = 614.4 kbytes /frame

Suppose the chip's peak throughput is 32Mbytes/sec total time to compress or decompress = 614.4 k /(32M) sec = 19.2 ms/frame

By adding 1.3ms due to initialization and some overhead, we will get 20.5 ms for VGA size YUV 4:2:2 one frame processing.

Based on the same consideration, we can get 81.92 ms for 2,621.44 kbyte data. With 1.1ms margin, the chip will take 83ms to process SVGA size YUV 4:2:2 one frame data.

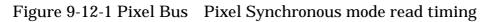

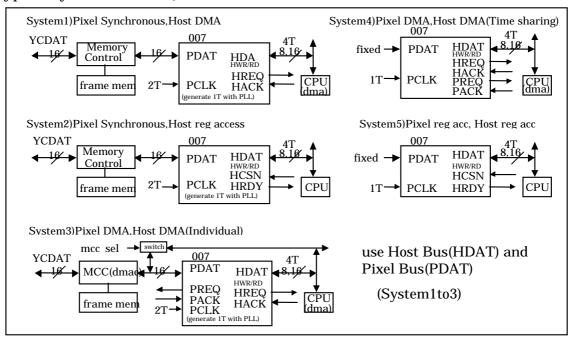

For pixel data transfer, user can select one of the following mode.

- PCLK synchronous mode (thru pixel bus)

- pixel DMA dedicated mode (thru pixel bus)

- pixel DMA timesharing mode (thru host bus)

- register access mode (thru host bus)

For code data transfer, either mode can be selected.

- host DMA mode (thru host bus)

- register access mode (thru host bus)

When choosing PCLK synch mode or pixel DMA dedicated mode, pixel data can be transferred in parallel with code data transfer. Both transfer uses the separated bus and user can make full use of the system hardware resources.

When using pixel DMA timesharing mode or register access mode, user accesses both pixel and code data through host bus.

User can select bus size (16bit or 8bit), endian (big or little) of pixel bus and host bus separately by setting the internal register bits.

Please note that pixel data is assumed to be transferred in block interleaved format. Number of components and relative sampling ratio are user selectable within JPEG baseline specification.

To reduce the power consumption in idle mode, user can stop the chip internal clock by asserting the external LOWPWR pin. Chip goes into low power mode.

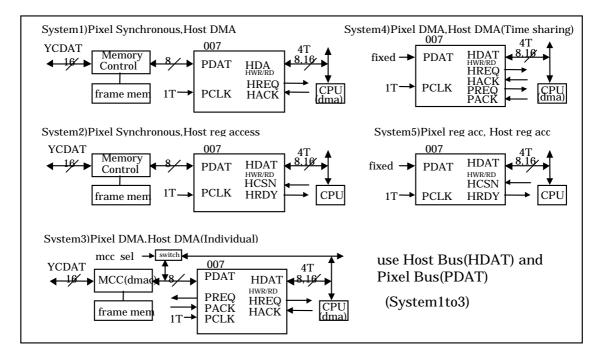

Chip is molded into the thin flat package LQFP with 0.5mm lead pitch. There are two types of LQFP package depending on user application.

For full use of KL5A71007 JPEG function, LQFP-80 (80pin, 12mm-sq mold size) is the best choice. Another selection is LQFP-64, which is smaller (10mm-sq mold size).

For LQFP-64, the PLL function is not available and the width of pixel bus is restricted to 8 bits to save the pin count.

2) Specification overview

KL5A71007 is designed under the following specification.

- a) compress/decompress method

- compliant with the JPEG standard baseline process<sup>4</sup> (ISO/IEC 10918-1)

- b) digital imaging data format

- each component has 8 bit data.

- endian selectable

- block interleaved format<sup>5</sup>

- unsigned or binary offset to be converted 2's compliment

- data is level shifted (-128) internally

- c) chip throughput

- max 32M bytes/sec at internal clock rate 32MHz

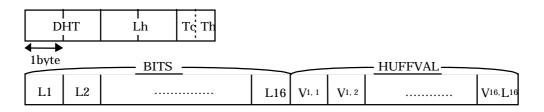

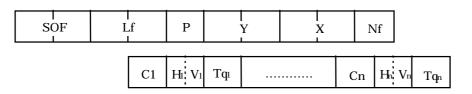

d) marker code to be processed

- for compression

SOI, DHT, DQT, DRI, SOF0, SOS, RSTm, EOI markers are generated and attached as header information.

- for decompression

SOI, DHT, DQT, DRI, SOF0, SOS, RSTm, EOI, DNL markers are decoded and used for data processing.

APPn followed by Lp bytes and COM followed by Lc bytes are completely ignored by the chip.

e) quantization table

- 4 sets of programmable table area (RAM, up to 4 components)

f) Huffman table

- 4 sets of programmable table area (RAM, 2 for DC table and 2 for AC table)

## g) table setting

- programmed by CPU through host interface or by reading the header data.

- header data can be used during compression

- data without table information can be decompressed by using presetting table data

#### h) input/output bus

- pixel bus

Used at PCLK synchronous mode and pixel DMA dedicated mode. Bus width is 8bits for LQFP-64 and 8bits/16bits selectable for LQFP-80.

- host bus

Used for code data transfer at register access mode or host DMA mode.

Also used for pixel data transfer at register access mode or pixel DMA timesharing mode.

#### i) input/output buffer

- LVTTL compatible buffer.

j) power voltage

- 3.3 volt +/- 0.3 volt

#### l) clock rate

- internal clock rate max 32 MHz

- external clock rate max 32 MHz (PLL no use) max 16 MHz (PLL use)

m) low power mode

- stop the internal clock

-----

- DCT-base process

- image data

8bits per component. Unsigned or binary offset.

Input data is level shifted (-128) internally.

- sequential coding (All components are coded into one scan)

- Huffman coding

2AC and 2DC tables

- Decoder

up to 4 components can be processed

- interleaved (Ns > 1) and non-interleaved (Ns = 1) scan

5) block interleaved format

Input data is grouped by component constructing block data which is corresponding to 8 by 8 pixel data. Then block data is interleaved. Each data in the block is sequentially transferred (from upper left to lower right).

<sup>4)</sup> JPEG baseline process

The basic feature of the JPEG baseline process is summarized as follows. (extracted from CCITT Rec. T.81 p.22)

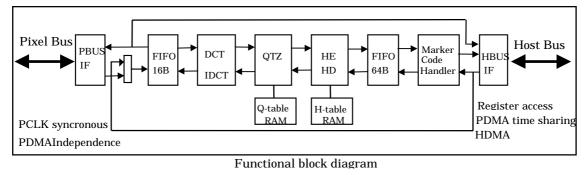

#### 3) Chip interface and reset operation

internal block diagram

chip function overview

Data processing flow is as follows.

In compress operation, pixel data in block interleaved format is fed in 16Byte FIFO through PBUS interface from pixel bus or through HBUS IF from host bus. Pixel data is converted to DCT coefficients by DCT/IDCT block. DCT coefficients are quantized by QTZ block, which use the quantize coefficient stored in Q-table RAM. Quantized DCT coefficients are converted to Huffman code by HE/HD block. Huffman code data is sent to 64Byte FIFO. With JPEG formatting (Marker attached), code data is out to the host bus

through HBUS IF.

In decompress operation, JPEG code data is sent to 64Byte FIFO via Marker Code Handler, where marker code is decoded and stripped. code data is Huffman decoded, de-quantized and inversely transformed to the pixel data. Pixel data is sent to 16Byte FIFO and out to the pixel bus through PBUS IF or to the host bus through HBUS IF.

Both Quantization coefficients and Huffman codec information are stored in RAM, where values are programmable and are set at the beginning of the operation by loading outside or extracting from the incoming JPEG data.

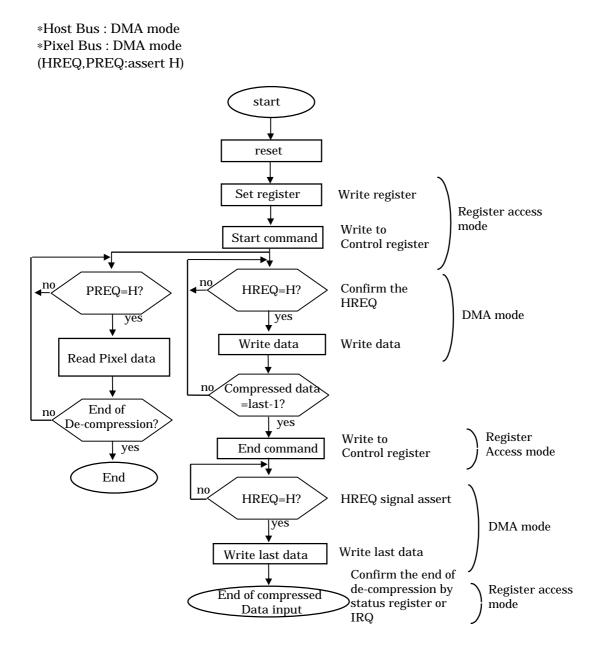

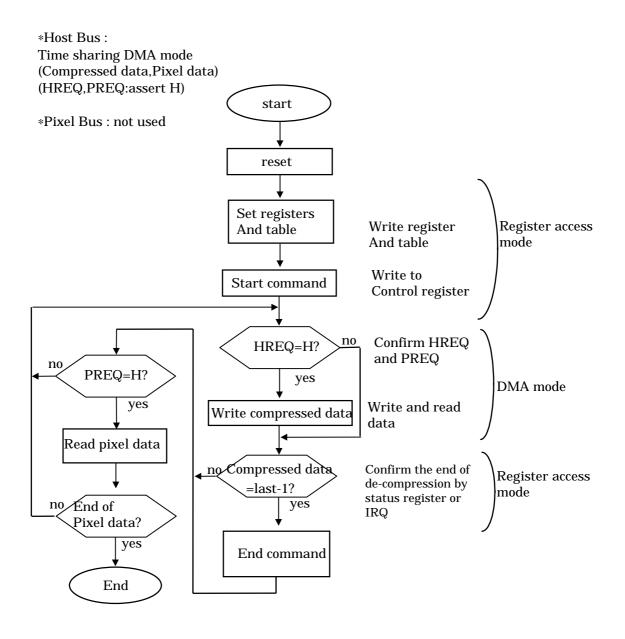

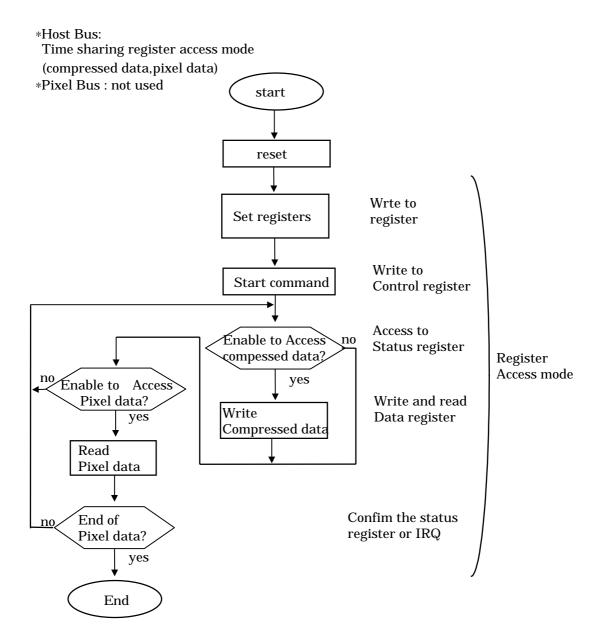

detail data transfer mode explanation

There are several mode to transfer the pixel and code data to/from outside. Four modes are presented for the pixel data transfer (a to d). Two modes (e and f) are shown for the code data transfer.

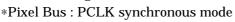

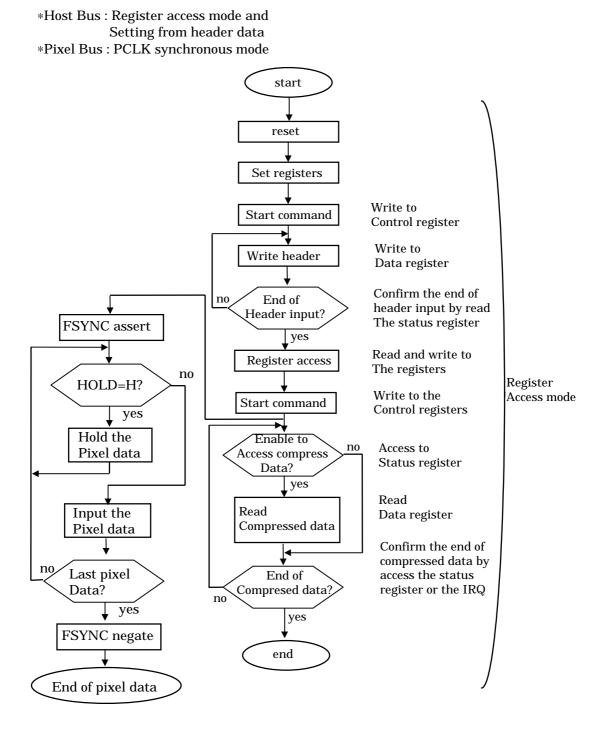

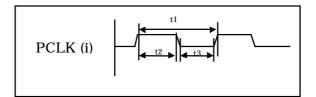

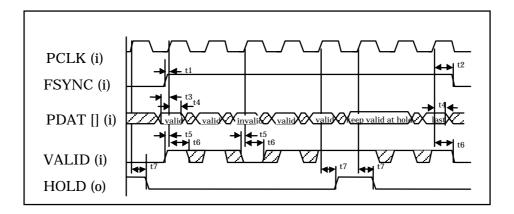

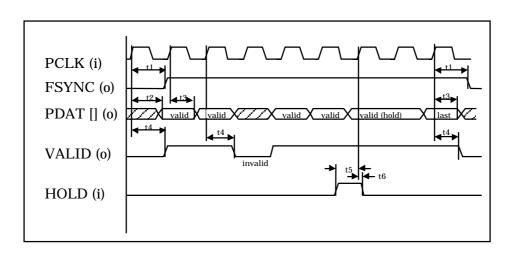

a) PCLK synchronous mode (thru pixel bus) - pixel transfer

With external PCLK, the pixel data is sent or received from the JPEG chip through pixel bus. Bus width can be changed 8bit (default) to 16bit by setting the internal register value. For 8bit operation, PCLK is used as the internal clock. For 16bit operation, internal PLL generates double frequency of PCLK, which is used as internal clock and the pixel data can be accessed continuously. Incoming or outgoing pixel data can be holded by VALID and HOLD handshake. Pixel data sender can stop sending data by negating VALID. Pixel data receiver can hold the incoming data by asserting HOLD signal. Both operation can be performed independently each other. Direction of pixel bus is determined by the flags in mode register (HADDR = h06). After the hardreset, pixel bus is set to the input direction.

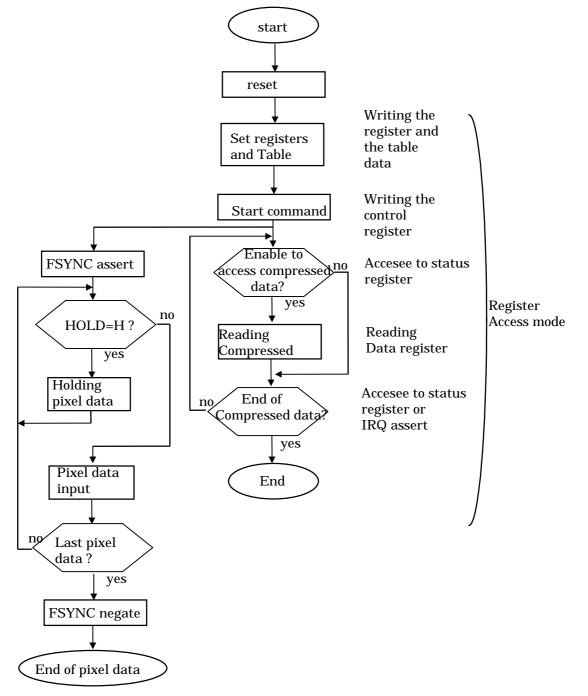

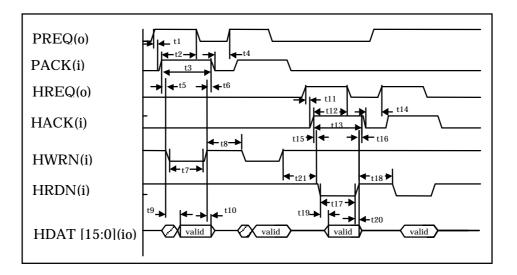

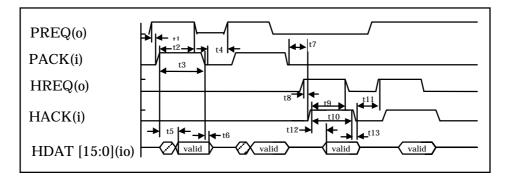

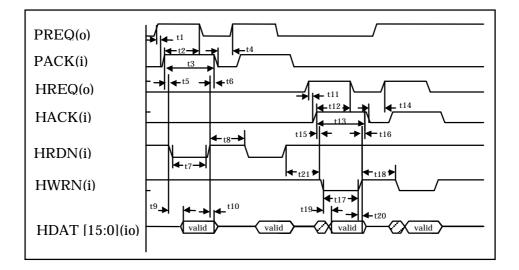

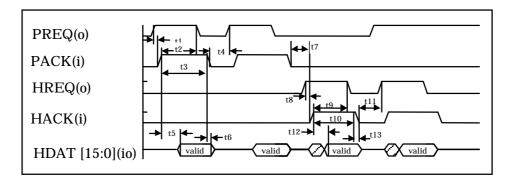

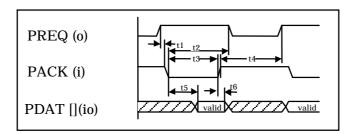

b) pixel DMA dedicated mode (thru pixel bus) - pixel transfer

Pixel bus can also be used as DMA bus. As slave DMA device, pixel data can be transferred with PREQ and PACK handshake.

DMA transfer is an asynchronous, which means no need to synchronize both pixel data and PACK signal with external chip clock. Both bus width and endian format can be selected by setting the bus format register (HADDR = h00). Internal clock is also selectable by using PLL as external clock doubler or by using the external clock itself.

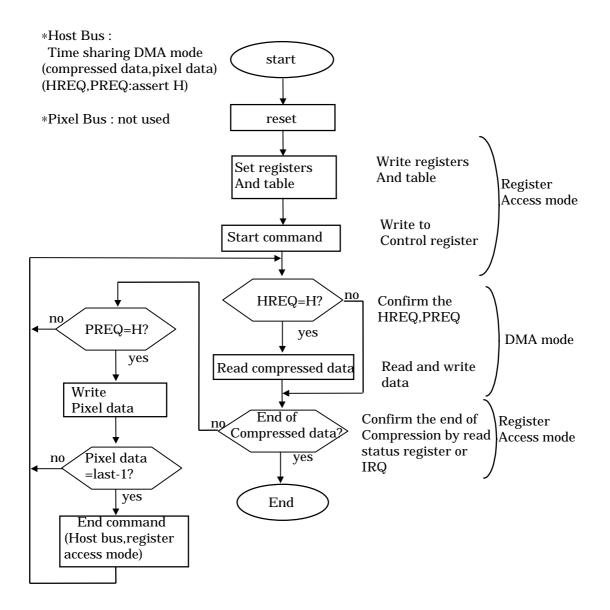

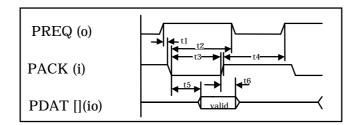

c) pixel DMA timesharing mode (thru host bus) - pixel transfer

Instead of using pixel bus, host bus can be used in pixel data DMA transfer. This is one of the host bus timesharing operation. Pixel data is transferred to the 16bit FIFO automatically in the chip. Pixel data DMA transfer through host bus is performed by PREQ and PACK handshake. User also can use HRDN and HWRN control signals in cope with PACK by selecting the flag of mode register (HADDR = h06). Bus width, it's endian format and internal clock generation method are the same as the description in b).

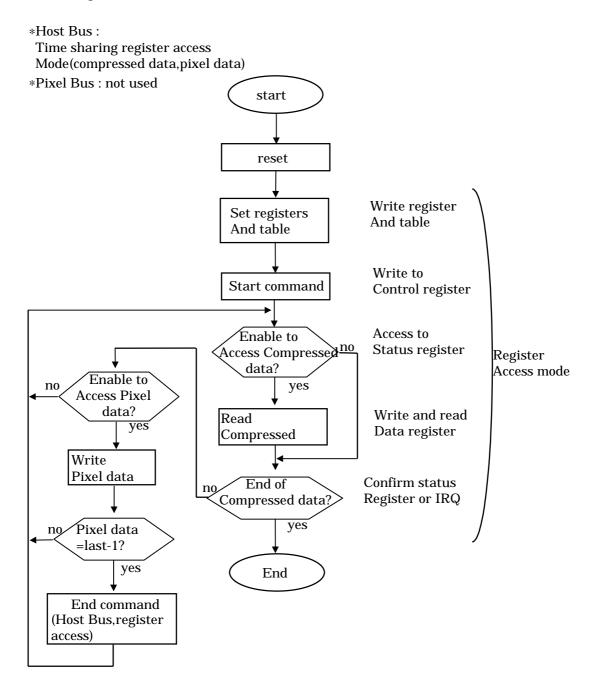

d) register access mode (thru host bus) - pixel transfer

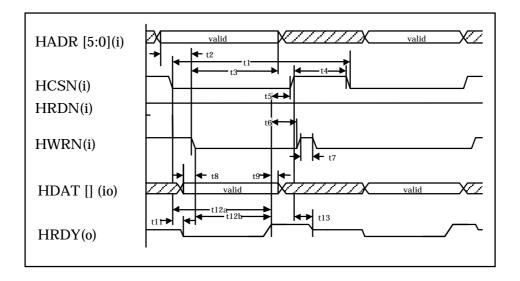

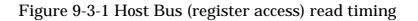

Pixel data can be transferred by using the register access mode through host bus in timesharing operation. External controller drives the pixel data register address (HADDR = h2E), asserts the control signal - HRDN or HWRN and transfers the pixel data. Transaction is not ended until asserting the HRDY signal by JPEG chip.

This HRDN/HWRN - HRDY handshake is exactly the same as that of JPEG

chip internal register access. To assure the correct operation, HRDY assertion is always verified by the external controller before the termination of transaction each time. It is strongly recommended that the external controller checks the status register (HADDR = h30) every time before accessing the pixel data register to see the pixel data is available or not. Otherwise the deadlock might occur because JPEG chip requires the code data to proceed the operation while the external controller is waiting for the ending of the pixel data transfer, which will never end due to the internal buffer full or empty.

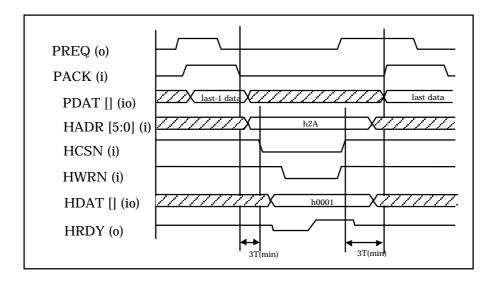

e) host DMA mode (thru host bus) - code transfer

Code data can be transferred by using host DMA mode through the host bus. Handshake is HREQ and HACK. As is the pixel DMA timesharing mode, HRDN or HWRN control or just HACK control is user selectable by choosing the mode register (HADDR = h06).

DMA transfer is the asynchronous to the external clock. The host bus width and endian format are set by the flag of the corresponding internal register. For internal clock generation, please refer to the description in b).

f) register access mode (thru host bus) - code transfer

Code date also can be transferred by using the register access mode. Its register address is h2C (code data register).

Treatment of HRDY and the method to avoid the deadlock described in pixel data transfer using register access mode section are also true here. Please refer to d) for detail discussion.

#### soft-reset operation

In addition to be reset by the external reset pin, the chip can be reset by setting the register bit with register access.

This operation is called "soft-reset". The register address of the corresponding register flag is h24. Please note that the data in the system registers is NOT cleared by the soft-reset operation.

#### lowpower operation

To save the power consumption when the chip is not in operation, external lowpower pin is useful. By pulling the LOWPWR pin to L, internal clock is stopped and the chip goes into the lowpower mode. It is strongly recommended to avoid lowpower setting during compress or decompress operation. When releasing the LOWPWR pin to H, the chip is recovered from the lowpower mode. Before doing the compress or decompress operation, soft-reset operation is required.

If internal PLL function is used by setting the MODE pins to an appropriate value, 2 msec lock-time is needed after the release of LOWPWR pin to guarantee the PLL lock-time. Then softreset is expected before starting the compress or decompress operation.

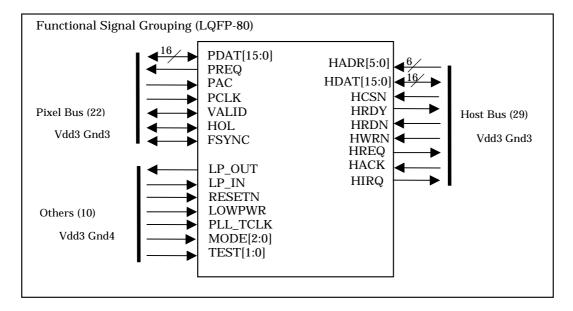

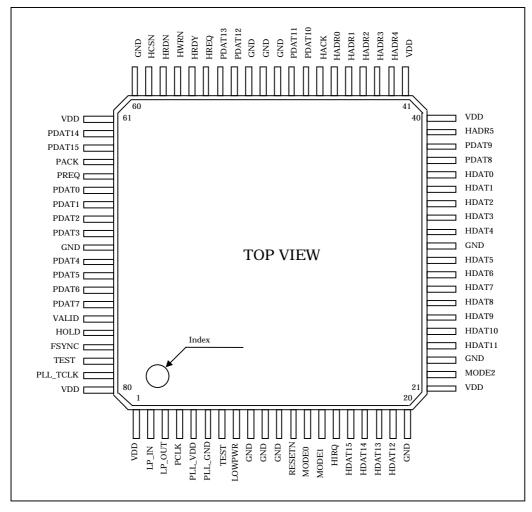

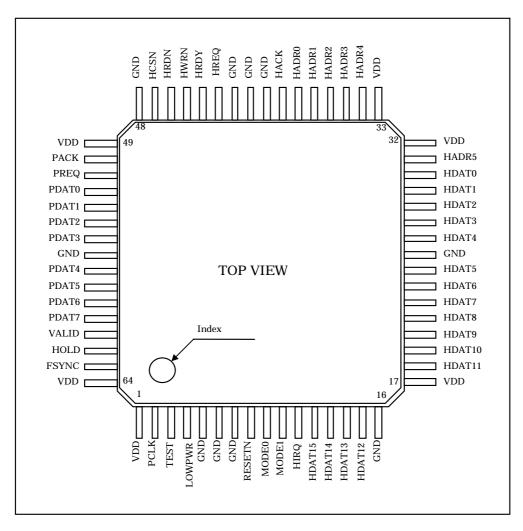

## 4) 80pin LQFP Pin Layout (LQFP-80)

## 4.1 Functional Signal Grouping

## 4.2 Pin Assignments (Top view)

## 5) Signal Descriptions(LQFP-80)

| No.   | Signal     | Pin                       | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|------------|---------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *Host | Bus        |                           |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1     | HADR[5:0]  | 39,<br>42-46              | Ι   | The HADR[5:0] are "Host Bus Address" signals and provide internal register address.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2     | HDAT[15:0] | 16-19,<br>24-30,<br>32-36 | I/O | The HDAT[15:0] are "Host Bus Data"<br>signals and used for transferring internal<br>register data, compressed data, and pixel<br>data in time sharing DMA mode and<br>register access mode.<br>Data bus width can be selected 16 bits<br>(word transferring) or 8 bits (byte<br>transferring) by internal register, which is<br>set 8 bits after hard reset.<br>In word transfer, endian format also can<br>be selected by internal register, which is set<br>little endian format after hard reset. LSB is<br>HDAT[0]. |

| 3     | HCSN       | 59                        | Ι   | The HCSN is "Host Bus Chip Select" and<br>active low signal. When asserted,<br>KL5A71007 recognizes as register access<br>mode.                                                                                                                                                                                                                                                                                                                                                                                         |

| 4     | HRDY       | 56                        | ОТ  | The HRDY is "Host Bus Ready" and active<br>high signal.<br>When asserted, it indicates the end of data<br>writing or the permission of data reading.<br>It is driven while HCSN is asserted.                                                                                                                                                                                                                                                                                                                            |

| 5     | HRDN       | 58                        | Ι   | The HRDN is "Host Bus Read Strobe" and<br>active low signal.<br>When asserted, reading operation is<br>executed. In register access mode, HDAT<br>are read at HRDY asserted timing.<br>In Host Bus DMA mode without HRDN<br>and HWRN, please connect to L.                                                                                                                                                                                                                                                              |

| 6     | HWRN       | 57                        | Ι   | The HWRN is "Host Bus Write Strobe" and<br>active low signal.<br>When asserted, writing operation is<br>executed. In register access mode, HDAT<br>are written at HRDY asserted timing.<br>In Host Bus DMA mode without HRDN<br>and HWRN, please connect to L.                                                                                                                                                                                                                                                          |

| 7     | HREQ       | 55                        | 0   | The HREQ is "Host Bus DMA Request" and<br>active high signal after hard reset.<br>In Host Bus DMA mode, HREQ is asserted<br>when data transfer is permitted, and<br>requires DMA access.<br>The Active level can be selected by internal<br>register.                                                                                                                                                                                                                                                                   |

| 8     | НАСК       | 47                        | Ι   | The HACK is "Host Bus DMA Acknowledg-<br>ment" and active high signal after hard<br>reset. When asserted, KL5A71007 negates<br>HREQ. In Host Bus DMA mode without<br>HRDN and HWRN, transfer is executed by<br>HACK only.<br>The active level can be selected by internal<br>register.                                                                                                                                                                                                                                  |

## 5) Signal Descriptions (LQFP-80)

| No.   | Signal     | Pin                                                     | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|------------|---------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *Host | Bus        |                                                         |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9     | HIRQ       | 15                                                      | 0   | The HIRQ is "Host Bus Interruption<br>Request" and active high signal after hard<br>reset.<br>When the event occurs which is<br>monitored by permission bits of IRQ flag<br>register, KL5A71007 sets IRQ flag bits<br>and asserts HIRQ.<br>After reading the IRQ register or reset,<br>the flag bits are cleared and HIRQ is<br>negated. In reset, permission bits are<br>also cleared.<br>The active level can be selected by<br>internal register.                                                                                                                                 |

| *Pixe | l Bus      |                                                         |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10    | PDAT[15:0] | 63-62,<br>54-53,<br>49-48,<br>38-37,<br>74-71,<br>69-66 | I/O | The PDAT[15:0] are "Pixel Data Bus"<br>signals and used for transferring pixel<br>data in PCLK synchronous mode and<br>individual DMA mode.<br>Data bus width can be selected 16 bits or<br>8 bits by internal register, which is set 8<br>bits after hard reset.<br>In word transfer, endian format also can<br>be selected by internal register, which is<br>set little endian format after hard reset.<br>In byte transfer, please connect upper<br>byte to H or L. Or in time sharing DMA<br>mode and register access mode, please<br>connect PDAT to H or<br>L. LSB is PDAT[0]. |

| 11    | PCLK       | 4                                                       | Ι   | The PCLK is "System Clock" signal.<br>KL5A71007 operates according to this<br>clock. In PCLK synchronous mode, Pixel<br>data is processed by every PCLK. When<br>LOWPWR is H, internal clock is stopped<br>and KL5A71007 enters low power mode<br>even though PCLK is given.                                                                                                                                                                                                                                                                                                         |

| 12    | VALID      | 75                                                      | I/O | The VALID is "PDAT Valid" and active<br>high signal. In PCLK Synchronous mode,<br>It is asserted by output side of PDAT and<br>indicates that PDAT are valid.<br>Except for PCLK Synchronous mode,<br>please connect to L.                                                                                                                                                                                                                                                                                                                                                           |

| 13    | HOLD       | 76                                                      | I/O | The HOLD is "PDAT Hold" and active<br>high signal.<br>In PCLK Synchronous mode, It is<br>asserted by input side of PDAT and<br>indicates that PDAT can not be received.<br>After negated, PDAT transfer<br>is resumed.<br>Except for PCLK Synchronous mode,<br>please connect to L.                                                                                                                                                                                                                                                                                                  |

## 5) Signal Descriptions (LQFP-80)

| No.   | Signal | Pin | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|--------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *Pixe | l Bus  |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 14    | FSYNC  | 77  | I/O | The FSYNC is "PCLK Synchronous<br>Transfer Period" and active high signal.<br>In PCLK Synchronous mode, It is<br>asserted from first data transfer to last<br>data transfer by output side of PDAT and<br>indicates that PDAT are transferred.<br>Except for PCLK Synchronous mode,<br>please connect to L.                                                                                                     |

| 15    | PREQ   | 65  | Ο   | The PREQ is "Pixel Bus DMA Request"<br>and active high signal after hard reset.<br>In Pixel Bus DMA mode both time<br>sharing and individual, PREQ is asserted<br>when data transfer is permitted, and<br>requires DMA access.<br>The active level can be selected by<br>internal register.                                                                                                                     |

| 16    | PACK   | 64  | Ι   | The PACK is "Pixel Bus DMA<br>Acknowledg-ment" and active high signal<br>after hard reset.<br>When asserted, KL5A71007 negates<br>PREQ.<br>In Pixel Data DMA mode both time<br>sharing and individual, DMA transfer is<br>executed by PACK<br>The active level can be selected by<br>internal register.                                                                                                         |

| *Othe | ers    | 1   | 1   |                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17    | LOWPWR | 8   | Ι   | The LOWPWR is "Low Power Mode<br>Trigger" and active high signal.<br>When LOWPWR is asserted, internal<br>system clock is stopped and power is<br>saved.<br>After negated, please execute soft reset.                                                                                                                                                                                                           |

| 18    | RESETN | 12  | Ι   | The RESETN is "Hard Reset", and active<br>low signal.<br>When RESETN is asserted, all registers<br>are cleared and KL5A71007 returns initial<br>state, and all bi-directional pins and 3-<br>state outputs become Hi-Z.<br>RESETN also works same operations in<br>low power mode.<br>The difference between hard reset and<br>soft reset is soft rest does not clear the<br>registers except for Error Report. |

## 5) Signal Descriptions (LQFP-80)

| No.   | Signal    | Pin          | I/O | Function                                                                                                                                                                                                                                                 |

|-------|-----------|--------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *Othe | ers       |              |     |                                                                                                                                                                                                                                                          |

| 19    | MODE[2:0] | 22,<br>14-13 | Ι   | The MODE[2:0] are "Chip Mode Control"<br>signals.<br>o b101 using PLL<br>o b001 not using PLL<br>If PLL is available, please input L to<br>MODE[2] until power become stable. After<br>that, please input H to MODE[2]. The lock<br>time for PLL is 2ms. |

| 20    | TEST[1:0] | 7,78         | Ι   | The TEST is "Test Mode Control" signal.<br>Please connect to GND.                                                                                                                                                                                        |

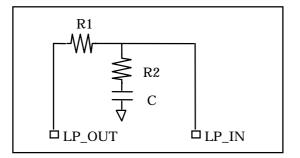

| 21    | LP_IN     | 2            | Ι   | The LP_IN and LP_OUT are "Off-Chip<br>Loop Filter Pin for PLL".<br>If internal PLL is available, off-chip loop<br>filter is needed to remove the high-                                                                                                   |

| 22    | LP_OUT    | 3            | 0   | frequency noise element as shown Fig. 5.1.<br>Otherwise, please connect LP_IN to GND,<br>and open LP_OUT.                                                                                                                                                |

| 23    | PLL_TCLK  | 79           | Ι   | PLL_TCLK is "PLL Test Clock". Please connect to GND.                                                                                                                                                                                                     |

| 24    | PLL_VDD   | 5            | VDD | PLL_VDD is "PLL Power Supply". Please connect to VDD.                                                                                                                                                                                                    |

| 25    | PLL_GND   | 6            | GND | PLL_GND is "PLL Ground supply". Please connect to GND.                                                                                                                                                                                                   |

Low pass filter diagram

Filter constant recommendation

| No. | items | value | unit |

|-----|-------|-------|------|

| 1   | R1    | 20    | kΩ   |

| 2   | R2    | 75    | kΩ   |

| 3   | С     | 0.01  | μF   |

Fig. 5.1 Off-chip Loop Filter diagram

The definitions of internal registers are indicated below. After hard reset, the registers are set up the (def) value. If there is no (def) shown, the registers are cleared to 0. In soft reset, the registers do not changed except for Error Report Register which is cleared to (def).

If the (def) value or once set up value is used, resetting is not needed. However resetting Huffman table is needed when DHT marker code is required in every compressed data.

|       | Register                                               | HADR      | field | Function bit         |                                                 |  |  |

|-------|--------------------------------------------------------|-----------|-------|----------------------|-------------------------------------------------|--|--|

| No.   | Name                                                   | [5:0]     | bit   | definition           | Function bit definition                         |  |  |

| *Inte | erface Set Up Reg                                      | ister     |       |                      | 1                                               |  |  |

|       |                                                        |           | 0     | Host Bus Width       | 1:16bit 0:8bit(def)                             |  |  |

|       |                                                        |           | 1     | Host Bus Endian      | 1:Big 0:Little(def)                             |  |  |

|       | Bus Mode[3:0]                                          | h00       | 1     | Format               |                                                 |  |  |

|       | Dus Mode[5.0]                                          | 1100      | 2     | Pixel Bus Width      | 1:16bit 0:8bit(def)                             |  |  |

| 1     |                                                        |           | 3     | Pixel Bus Endian     | 1:Big 0:Little(def)                             |  |  |

|       |                                                        |           | -     | Format               |                                                 |  |  |

|       |                                                        |           |       |                      | Pixel Bus is 8 bits. If bit [0] is 1, even      |  |  |

|       |                                                        |           |       | In that case, Endian | Format is followed by bit [1]. For              |  |  |

|       | Endian Fo                                              | rmat, see |       |                      | 1                                               |  |  |

|       |                                                        |           | 0     | HREQ active level    | 1:assert H(def) 0:assert L                      |  |  |

|       | Signal Active                                          |           | 1     | HACK active level    | 1:assert H(def) 0:assert L                      |  |  |

| 2     | Level[4:0]                                             | h02       | 2     | PREQ active level    | 1:assert H(def) 0:assert L                      |  |  |

|       | Leveling                                               |           | 3     | PACK active level    | 1:assert H(def) 0:assert L                      |  |  |

|       |                                                        |           | 4     | HIRQ active level    | 1:assert H(def) 0:assert L                      |  |  |

| 3     | PDATuse [0]                                            | h04       | 0     | PDAT use             | 1:use 0:not use(def)                            |  |  |

| *Init | ial Set Up Regist                                      | er        |       |                      |                                                 |  |  |

|       |                                                        |           | 0     | Compression/         | 1:Compression(def)                              |  |  |

|       |                                                        |           | 0     | Decompression        | 0:Decompression                                 |  |  |

|       |                                                        |           | 1     | Header Informa-      | 1:by Registers(def)                             |  |  |

|       |                                                        |           | 1     | tion Loading         | 0:by JPEG Header                                |  |  |

|       |                                                        |           | 2     | Compressed Data      | 1:enable(def)                                   |  |  |

|       | Mode                                                   | h06       | ~     | Output Enable        | 0:disable                                       |  |  |

|       | Specify[6:0]                                           | 1100      |       | Compressed Data      | 0,1:Register Access(def 0)                      |  |  |

|       |                                                        |           | 4-3   | Transfer Mode        | 2:DMA(with HRDN and HWRN)                       |  |  |

| 4     |                                                        |           |       |                      | 3:DMA(without HRDN and HWRN)                    |  |  |

|       |                                                        |           |       | Pixel Data           | 0:Register Access(def)                          |  |  |

|       |                                                        |           | 6-5   | Transfer Mode        | 1:PCLKSynchronous                               |  |  |

|       |                                                        | (         |       |                      | 2,3:DMA                                         |  |  |

|       | Note: Pixel Data                                       |           |       | PDAT use[0]          | Mode Specify[6:5]                               |  |  |

|       |                                                        | er Access |       | bx                   | h0<br>h1                                        |  |  |

|       |                                                        | Synchror  |       | bx<br>b1             | h1<br>h2 or h3                                  |  |  |

|       | Individual DMA (PDAT use)<br>Time Sharing DMA (PDAT no |           |       |                      | h2 or h3<br>h2 or h3(same as Mode Specify[4:3]) |  |  |

|       |                                                        | g DMA (I  |       | JUUSE) DU            | nz or no(same as mode specify[4:3])             |  |  |

|       |                                                        |           |       |                      |                                                 |  |  |

| No.    | Register<br>Name                         | HADR<br>[5:0]           | field<br>bit | Function bit<br>definition               | Function bit definition                                                                                                     |

|--------|------------------------------------------|-------------------------|--------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| *Initi | ial Set Up Regist                        | er                      |              |                                          |                                                                                                                             |

| L      | Limit Of<br>Compressed                   | h08                     | 7-0          | Lower Byte of<br>Limit                   | unit is 1 K bytes<br>(from 0 K bytes to 255 K bytes)                                                                        |

| 5      | Data Volume<br>[15:0]<br>(k bytes)       | h09                     | 7-0          | Upper Byte of<br>Limit                   | unit is 256 K bytes<br>(from 0 K bytes to 64 M bytes)                                                                       |

|        | outputting HDA                           | T but cor               | ntinues      | internal operation.                      | reaches this limit, KL5A71007 stops<br>71007 does not stop outputting.                                                      |

|        |                                          | ,,                      | 1-0          | Output format                            | 0:normal(def) 1:normal<br>2:only header 3:only ECS                                                                          |

| 6      | Compressed<br>Data                       | h0A                     | 2            | DHT Output<br>Enable                     | 1:enable(def) 0:disable                                                                                                     |

| 0      | Format[3:0]                              | h0A                     | 3            | DQT Output<br>Enable                     | 1:enable(def) 0:disable                                                                                                     |

| *Tab   | le Set Up Registe                        | r                       |              |                                          |                                                                                                                             |

|        | Table Data<br>[7:0] (byte),              | h10                     | 7-0          | Table data transfer by byte              | H,Q table data set up by byte                                                                                               |

| 7      | [15:0] (word)<br><write only=""></write> | 1110                    | 15-0         | Table data transfer by word              | H,Q table data set up by word                                                                                               |

| 1      | data byte is                             | odd, the<br>gister. The | extra by     | yte of last word data i                  | input. In word access, if number of<br>s ignored. Endian format is followed by<br>ept for table data setting up by register |

| *Hea   | der Information                          | Register                |              |                                          |                                                                                                                             |

|        | Restart                                  | h12                     | 7-0          | DRI lower byte                           | DRI lower byte(7:0) (0:def)                                                                                                 |

| 8      | Interval[15:0]                           | h13                     | 7-0          | DRI upper byte                           | DRI upper byte(15:8) (0:def)                                                                                                |

|        | Note:When set                            | up 0, DRI               | and RS       | T markers are not ad                     | ded in compressed data.                                                                                                     |

| 0      | Number of                                | h14                     | 7-0          | Number of lines<br>lower byte            | Number of lines lower byte<br>(7:0) (0:def)                                                                                 |

| 9      | Lines<br>(SOF;Y)[15:0]                   | h15                     | 7-0          | Number of lines<br>upper byte            | Number of lines upper byte<br>(15:8) (0:def)                                                                                |

| 10     | Number of<br>Samples Per                 | h16                     | 7-0          | Number of samples<br>per line lower byte | Number of samples per line lower<br>byte (7:0) (1:def)                                                                      |

| 10     | Line (SOF;X)<br>[15:0]                   | h17                     | 7-0          | Number of samples<br>per line upper byte | Number of samples per line upper<br>byte (15:8) (0:def)                                                                     |

|        | Number of<br>Image                       |                         | 2-0          | No. of components<br>in Frame (Nf)       | Defined in 1(def) - 4                                                                                                       |

| 11     | Components<br>(SOF;Nf,SOS;<br>Ns)[15:0]  | h18                     | 5-3          | No. of components<br>in Scan (Ns)        | Defined in 1(def) - 4                                                                                                       |

| No.  | Register<br>Name<br>der Information | HADR<br>[5:0] | field<br>bit | Function bit definition          | Function bit definition             |

|------|-------------------------------------|---------------|--------------|----------------------------------|-------------------------------------|

| *Hea |                                     | h1A           | 7-0          | Component identifier<br>C1       | 0-255(def 0)                        |

| 12   | SOF 1st<br>Component<br>Information |               | 1-0          | Horizontal Sampling<br>Factor H1 | 0:H1=4 1:H1=1(def)<br>2:H1=2 3:H1=3 |

|      | [13:0]                              | h1B           | 3-2          | Vertical Sampling<br>Factor V1   | 0:V1=4 1:V1=1(def)<br>2:V1=2 3:V1=3 |

|      |                                     |               | 5-4          | Q table selector Tq1             | 0-3(def 0)                          |

|      |                                     | h1C           | 7-0          | Component identifier<br>C2       | 1-255(def 1)                        |

|      | SOF 2nd                             |               | 1-0          | Horizontal Sampling<br>Factor H2 | 0:H1=4 1:H1=1(def)<br>2:H1=2 3:H1=3 |

| 13   | Component<br>Information            | h1D           | 3-2          | Vertical Sampling<br>Factor V2   | 0:V1=4 1:V1=1(def)<br>2:V1=2 3:V1=3 |

|      | [13:0]                              |               | 5-4          | Q table selector Tq2             | 0-3(def 0)                          |

|      |                                     | h1E           | 7-0          | Component identifier<br>C3       | 2-255(def 2)                        |

| 14   | SOF 3rd<br>Component<br>Information |               | 1-0          | Horizontal Sampling<br>Factor H3 | 0:H1=4 1:H1=1(def)<br>2:H1=2 3:H1=3 |

|      | [13:0]                              | h1F           | 3-2          | Vertical Sampling<br>Factor V3   | 0:V1=4 1:V1=1(def)<br>2:V1=2 3:V1=3 |

|      |                                     |               | 5-4          | Q table selector Tq3             | 0-3(def 0)                          |

|      |                                     | h20           | 7-0          | Component identifier<br>C4       | 3-255(def 3)                        |

| 15   | SOF 4th<br>Component                | h21           | 1-0          | Horizontal Sampling<br>Factor H4 | 0:H1=4 1:H1=1(def)<br>2:H1=2 3:H1=3 |

|      | Information<br>[13:0]               |               | 3-2          | Vertical Sampling<br>Factor V4   | 0:V1=4 1:V1=1(def)<br>2:V1=2 3:V1=3 |

|      |                                     |               | 5-4          | Q table selector Tq4             | 0-3(def 0)                          |

| No.  | Register Name                                                               | HADR<br>[5:0] | field<br>bit | Function bit<br>definition          | Function bit definition                                             |  |  |  |

|------|-----------------------------------------------------------------------------|---------------|--------------|-------------------------------------|---------------------------------------------------------------------|--|--|--|

| *Hea | der Information R                                                           |               | DIC          | definition                          |                                                                     |  |  |  |

|      | SOS 1st<br>Component                                                        |               | 1-0          | Scan component<br>selector Cs1      | 0:Cs1=C1(def)<br>1:Cs1=C2<br>2:Cs1=C3<br>3:Cs1=C4                   |  |  |  |

|      | Information<br>[3:0]                                                        |               | 2            | DC table selector<br>Td1            | 0-1(def 0)                                                          |  |  |  |

|      |                                                                             |               | 3            | AC table selector<br>Ta1            | 0-1(def 0)                                                          |  |  |  |

|      | SOS 2nd                                                                     | h22           | 5-4          | Scan component<br>selector Cs2      | 0:not allowed by JPEG spec<br>1:Cs2=C2(def)<br>2:Cs1=C3<br>3:Cs1=C4 |  |  |  |

|      | Component<br>Information<br>[7:4]                                           |               | 6            | DC table selector<br>Td2            | 0-1(def 0)                                                          |  |  |  |

| 16   | [7.3]                                                                       |               | 7            | AC table selector<br>Ta2            | 0-1(def 0)                                                          |  |  |  |

|      | SOS 3rd                                                                     |               | 1-0          | Scan component<br>selector Cs3      | 0-1:not allowed by JPEG spec<br>2:Cs3=C3(def)<br>3:Cs3=C4           |  |  |  |

|      | Component<br>Information<br>[3:0]                                           | h23           | 2            | DC table selector<br>Td3            | 0-1(def 0)                                                          |  |  |  |

|      |                                                                             |               | 3            | AC table selector<br>Ta3            | 0-1(def 0)                                                          |  |  |  |

|      | SOS 4th                                                                     |               | 5-4          | Scan component<br>selector Cs4      | 0-2:not allowed by JPEG spec<br>3:Cs4=C4(def)                       |  |  |  |

|      | Component<br>Information                                                    |               | 6            | DC table selector<br>Td4            | 0-1(def 0)                                                          |  |  |  |

|      | [15:12]                                                                     |               | 7            | AC table selector<br>Ta4            | 0-1(def 0)                                                          |  |  |  |

| *Con | trol and Data Regi                                                          | ster          | 1            |                                     |                                                                     |  |  |  |

| 17   | Soft Reset[0]                                                               | h24           | 0            | Soft reset command                  | 1:execute<br>0:auto clear(def)                                      |  |  |  |

| 19   | Compression/<br>Decompression<br>Start Command<br>[0]                       | h28           | 0            | Start command                       | 1:execute<br>0:auto clear(def)                                      |  |  |  |

| 20   | Compression/<br>Decompression<br>End<br>Command[0]                          | h2A           | 0            | End command                         | 1:execute<br>0:auto clear(def)                                      |  |  |  |

| 0.1  | Compressed                                                                  | hac           | 7-0          | Compressed Data<br>transfer by byte | compressed data by byte                                             |  |  |  |

| 21   | Data[7:0](byte),<br>[15:0](word)                                            | h2C           | 15-0         | Compressed Data<br>transfer by word | compressed data by word                                             |  |  |  |

|      | Pixel Data<br>[7:0](byte),                                                  | h2E           | 7-0          | Pixel Data transfer<br>by byte      | pixel data by byte                                                  |  |  |  |

| 22   | [7:0](byte),<br>[15:0](word)                                                | II&Ľ          | 15-0         | Pixel Data transfer<br>by word      | pixel data by word                                                  |  |  |  |

|      | Note:This register is effective when pixel bus transfer is register access. |               |              |                                     |                                                                     |  |  |  |

| No.                                                                                                                                                                                                   | gisters<br>Register                 | HADR                  | field                | Function bit                                                        | Function bit definition                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------|----------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                       | Name                                | [5:0]                 | bit                  | definition                                                          | i unction bit definition                                                                                                                                                                                                                                                                                                                                                                             |

| *Rep                                                                                                                                                                                                  | ort Register                        |                       |                      | 1                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                       |                                     |                       | 0                    | Busy status                                                         | 1:busy 0:idle(def)                                                                                                                                                                                                                                                                                                                                                                                   |

| 23                                                                                                                                                                                                    | Status[3:0]                         | h30                   | 1                    | Compressed data<br>Access                                           | 1:allowed 0:not(def)                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                       | (read only)                         |                       | 2                    | Pixel data Access                                                   | 1:allowed 0:not(def)                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                       |                                     |                       | 3                    | Error status                                                        | 1:error(see h36) 0:normal(def)                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                       |                                     |                       | 0                    | Data output ready                                                   | 1:ready 0:flag reset(def)                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                       |                                     |                       | 1                    | Last data output end                                                | 1:end 0:flag reset(def)                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                       | IRQ Flag[7:0]                       |                       | 2                    | Overflow<br>compressed data<br>limit                                | 1:overflow 0:flag reset(def)                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                       | (read only                          | h32                   | 3                    | Error occur                                                         | 1:error 0:flag reset(def)                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                       | [3:0])                              |                       | 4                    | Permission for bit[0]                                               | 1:permit 0:not(def)                                                                                                                                                                                                                                                                                                                                                                                  |

| 24                                                                                                                                                                                                    |                                     |                       | 5                    | Permission for bit[1]                                               | 1:permit 0:not(def)                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                       |                                     |                       | 6                    | Permission for bit[2]                                               | 1:permit 0:not(def)                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                       |                                     |                       | 7                    | Permission for bit[3]                                               | 1:permit 0:not(def)                                                                                                                                                                                                                                                                                                                                                                                  |

| assert HIRQ. After hard reset, IRQ flag and HIRQ are cleared. I<br>only. They and HIRQ are cleared after IRQ Flag register read a<br>the overflow from the limit of compressed data volume, setting b |                                     |                       |                      | er read automatically. To confirm                                   |                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                       | Compressed<br>Data Volume           | h34                   | 7-0                  | Compressed data<br>volume lower byte                                | (The 10th-17th power of two)                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                       | [15:0](kbytes,                      | h35                   | 7-0                  | Compressed data                                                     | Less than 64MB, 256kB step                                                                                                                                                                                                                                                                                                                                                                           |

| 25                                                                                                                                                                                                    | read only)                          | 1155                  | 7-0                  | volume upper byte                                                   | (The 18th-25th power of two)                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                       | Compressed<br>Data Volume           | h3E                   | 7-0                  | Compressed data<br>volume lower byte                                | less than 256B, 1B step<br>(The 0th-7th power of two)                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                       | [15:0](bytes,                       |                       | 1.0                  | Compressed data                                                     | Less than 1kB, 256B step                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                       | read only)                          | h3F                   | 1-0                  | volume upper byte                                                   | (The 8th-9th power of two)                                                                                                                                                                                                                                                                                                                                                                           |

| 26                                                                                                                                                                                                    | Error<br>Report[7:0]<br>(read only) | h36                   | 7-0                  | Error report<br>(All error occurs in<br>decompression<br>except h1) | h0:no errors(def)<br>h1:overflow from the limit of<br>compressed data volume<br>(Compression)<br>h2:restart interval differ from DRI<br>h4:mismatch component ID<br>between SOS and SOF<br>h8:number of blocks per MCU is<br>more than 11<br>h10:header parameter does not<br>match JPEG baseline standard<br>h20:marker segment length error<br>h40:unknown marker code<br>h80:huffman decode error |

|                                                                                                                                                                                                       | and h80, KL5A<br>reset is needed    | 71007 can<br>to recov | n not op<br>er. If E | erate any more. In thi                                              | set 1. If Error report is between h2<br>s case, initializing by hard or soft<br>Status Register [3] is set 1. This                                                                                                                                                                                                                                                                                   |

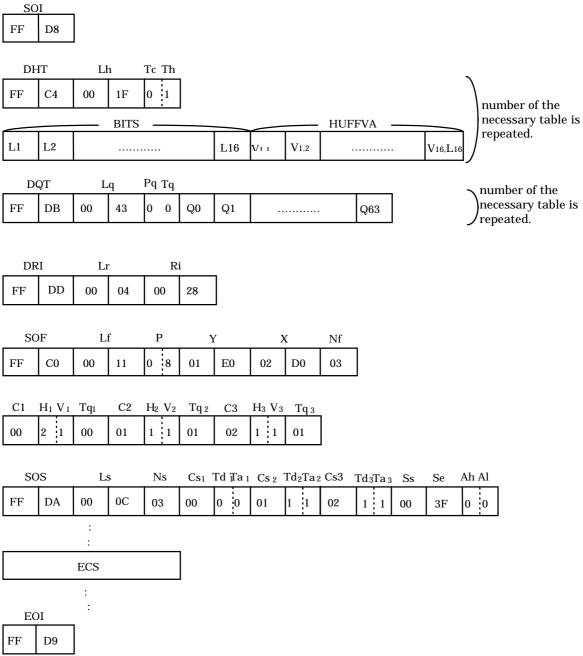

#### 7.1 Power On

After power on, hard reset is needed. And then, please establish "Interface Set Up registers" from Host Bus by register access mode. The value of system registers is not cleared by soft reset but hard reset.

In case of using PLL, please connect MODE[2] pin to L at power on, and connect H after power become stable. Next, please execute soft reset after 2ms lock time.

7.2 How To Establish "Initial Set Up Registers"

Firstly, to establish 'Mode Specify' register (address:h06) is needed for designation of operation and transferring way. Some examples are shown below.

| Pixel bus           | Host bus S            | SR04[0] | SR06[6:3] |

|---------------------|-----------------------|---------|-----------|

| a) PCLK synchronous | DMA with HRDN, HWRN   | b1      | b6        |

| b) Individual DMA   | DMA with HRDN, HWRN   | b1      | hA        |

| c) Time sharing DMA | DMA without HRDN, HWI | RN b0   | hF        |

| d) register access  | register access       | b0      | h0        |

To set up 'Mode Specify' register is also needed to determine compression or decompression, and data output enable in compression.

And to set up 'Compressed Data Format' register (address:h0A) is needed to determine compressed data output format, and output enable of table information.

'Limit Of Compressed Data Volume' registers (address:h09,h08) are needed to determine the limit of output data volume in compression. The unit is K byte. If data volume is over this limit, KL5A71007 stops outputting and continues internal compress operation. The right data volume is registered in 'Compressed Data Volume' register (address:h35,h34) whether the volume is over the limit or not.

#### 7.3 How To Establish "Table Data"

For establishing table data, writing table data to 'Table Data' register (address:h10) is needed, except for establishing by compressed data with table data. DHT and DQT marker code segment is required for written data. KL5A71007 checks the table definition length. When define the Haffman table, the register address h06 and h0A must be fixed.

In compression, if table data is required in each compressed data, table data have to be set up in every flame compression.

For only table data, continuative writing mode which can transfer plural data during one HCSN asserted period, can be used.

#### 7.4 Set up the Header information

Before compression, write the header information to the register in register access mode. The address is from h12 to h18 and h1A to h23. Compression is done with this information.

If set the value except 0 to the register h12 and h13, the restart interval maker (RST) will add to the compressed data.

In de-compression mode, header information is set to these registers.

#### 7.5 Compression

This section describes the compression operation with setting up described in 7.2 to 7.4. This chip will start operation when set the Start Register (register h28). If change the registers after starting the operation, This chip will not operate correctly. Register information can be read during the operation, so the status or IRQ information can be checked.

After starting this chip, the header data will be output. Read the data with asserting the HACK signal after the HREQ signal is asserted in HOST-DMA mode. In register access mode, read data from the compression data register (register address = h2C) after confirming the access flag can be accessed of the compression data of the status register (register address = h30).

When the output of the header data is completed, writing the pixel data becomes possible. In the PCLK synchronous mode after confirming the HOLD signal negated, assert FSYNC and VALID, and write the pixel data. In pixel DMA mode, after confirming the PREQ signal is asserted write the pixel data with assert the PACK signal. Write the image data in the image data register (register address = h2E) for the register access mode after confirming being able to access the register by reading the status register (register address = h30).

The output of the compression data starts from the host bus after about 180-240CLK after beginning writing the pixel data. Latency changes according to whether the access mode and the pixel data are continuously written. The access method is the same as the case of the output of the header data.