# Motion JPEG Chip KL5A72002 datasheet

Rev 0.8

Preliminary

Kawasaki Steel Corporation LSI division

#### 1. Revision history

| Rev | date     | The contents of updating |

|-----|----------|--------------------------|

| 0.1 | 98.12.17 | First release            |

| 0.8 | 99.12.20 | Release as KL5A72002     |

# 2. Notes

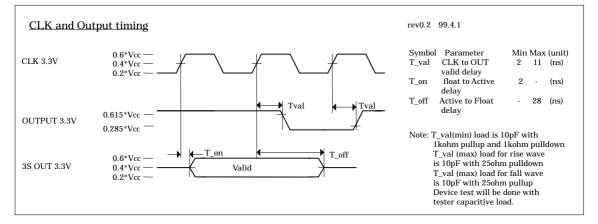

This document is preliminary version and may be changed without notice.

Kawasaki Steel Corporation reserves the right to make changes to the specifications herein at any time without notice.

Kawasaki Steel Corporation does not assume any responsibility or liability arising out of the application or use of any circuit or information described herein; neither does it convey any license under its patent rights, intellectual property rights, or any other rights of Kawasaki Steel Corporation or of third parties.

Please refer to each datasheet for detail information about JPEG and SDRAM.

# 3. Content

| 4.           | functional specification 4                       |       |  |  |  |  |  |  |  |  |

|--------------|--------------------------------------------------|-------|--|--|--|--|--|--|--|--|

| 5.           | pin and signal information                       | 10    |  |  |  |  |  |  |  |  |

| 6.           | package pin asignment (6A: FBGA176, 6B: LQFP176) | 11,13 |  |  |  |  |  |  |  |  |

| 7.           | package pin list (7A: FBGA176, 7B: LQFP176)      |       |  |  |  |  |  |  |  |  |

| 8.           | pin specification                                |       |  |  |  |  |  |  |  |  |

| 9.           | state transition diagram                         |       |  |  |  |  |  |  |  |  |

| 10.          | operation timing outline                         |       |  |  |  |  |  |  |  |  |

| 11.          | evaluation board                                 | 25    |  |  |  |  |  |  |  |  |

| 12.          | memory map                                       |       |  |  |  |  |  |  |  |  |

| 1            | 2.1 PCI configuration space                      | 27    |  |  |  |  |  |  |  |  |

| 1            | 2.2 Memory Mapping space (MCORE register)        | 33    |  |  |  |  |  |  |  |  |

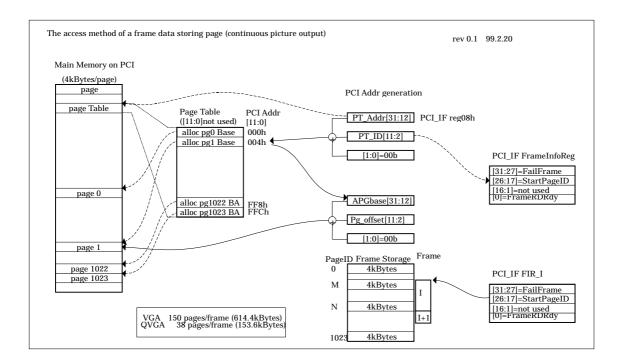

| 1            | 2.3 Frame Memory map                             | 45    |  |  |  |  |  |  |  |  |

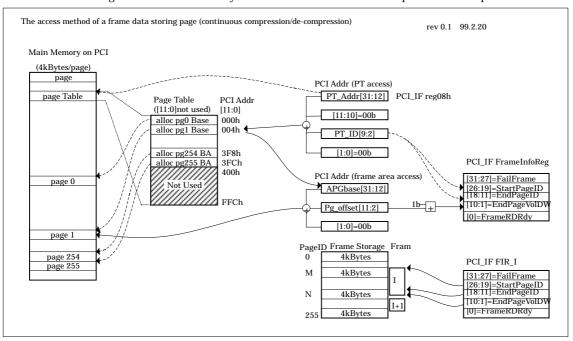

| 1            | 2.4 Main Memory Access Method (PCI Master        |       |  |  |  |  |  |  |  |  |

|              | Operation of Continuation Processing)            | 47    |  |  |  |  |  |  |  |  |

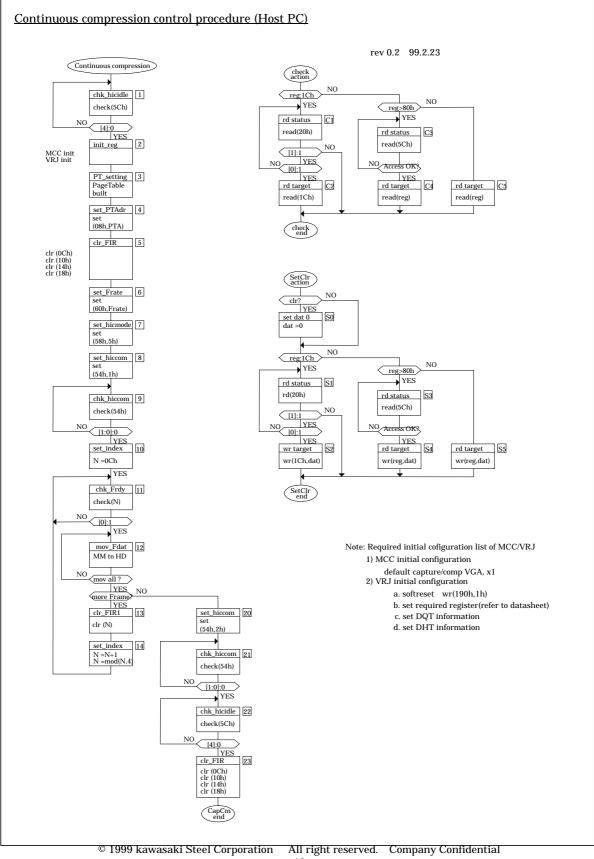

| 13. o        | levice control flow                              | 49    |  |  |  |  |  |  |  |  |

| 14. e        | 14. example of initial setting 50                |       |  |  |  |  |  |  |  |  |

| 15. <b>e</b> | 15. electric specification                       |       |  |  |  |  |  |  |  |  |

| 16. p        | 16. package outline                              |       |  |  |  |  |  |  |  |  |

| 17. ł        | 17. known bug 65                                 |       |  |  |  |  |  |  |  |  |

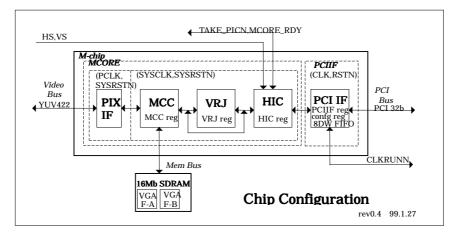

# 4. Functional specification

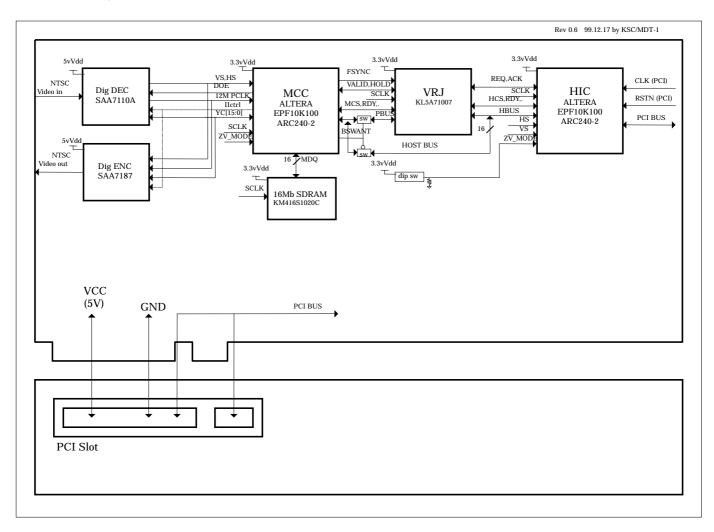

PIX IF : pixel data interface

- MCC : SDRAM controller

- VRJ : high speed JPEG (KL5A71007)

- HIC : host interface, chip controller

PCI IF : PCI interface

# 4.1 Through image display (only in digital YC mode)

Register setting to external digital video codec and YCDATA transfer from Decoder to Encoder

#### 4.2 Frame memory control

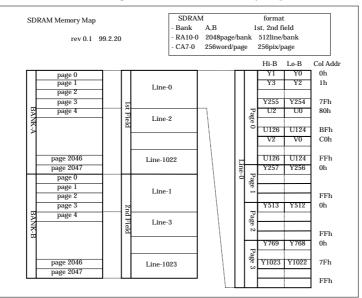

- Initial setting to frame memory (SDRAM 1M x 16b), set refresh and lowpower

- Target SDRAM is KM416S1120, 512K X 16Bit X 2 Banks 100MHz or Equivalent Article

- Perform auto refresh 5 times / 1H synchronizing with rising edge of HS

- When the pulse interval of HS becomes more than 66 $\mu$ sec, refreshment timing is automatically calculated inside and refreshment of SDRAM is continued at 5 times every 66  $\mu$ sec.

- When LSI is set as the low power mode, a power down setup is performed to SDRAM and it

is set as the low power-consumption mode. The data of SDRAM are lost at this time.

4.3 Frame memory access

- Direct writing and read out to/from SDRAM

- Access SDRAM through the register of MCC block in PCI target mode.

- Possible to access linear and continuously from set-up initial address to Memory Space.

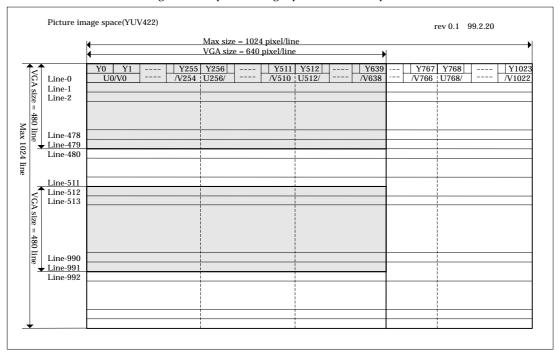

- 1024 pixel x 1024 line(max), YUV=422 image is stored in frame memory

- In motion processing mode, 2 VGA size image is processed alternatively

- 4.4 Still image capture

- Capture 1 frame still image(YUV=422)

- Selectable 2 mode video bus interface

ZV-port mode : YUV=422, progressive VGA image input

# YC[15:0], HS, VS, PCLK

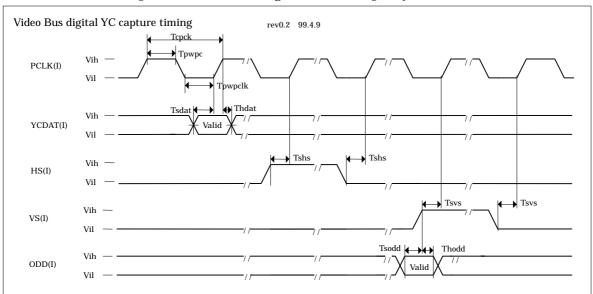

#### Digital YC mode : YUV=422 interlace VGA image input

#### YC, HS, VS, PCLK, ODD, DOE

- Capture position and range is set to register as H\_(V\_)START and H\_(V\_)COUNT.

- 1/2 sub-sampling both horizontal and vertical is possible during image capture.

- The execution timing of a command synchronizes with VS which shows frame start.

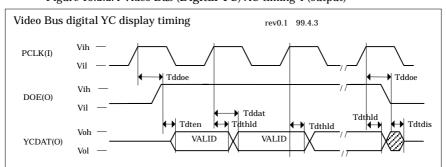

- 4.5 Display (only in digital YC mode)

- Display image stored in frame memory

- Displayed image area is set to register, R\_X(Y)BASE and R\_X(Y)RANGE

- Continue display untill the stop display command (NO DISP) is execute

- The execution timing of a command synchronizes with VS of the first field.

- 4.6 JPEG Independent Compression

- Pixel data of block interleave format is written to the chip in PCI target mode and compressed with an internal JPEG core and JPEG compression data is output in PCI target mode, time shared with pixel data.

- 4.7 JPEG Independent de-compression

- JPEG compression data is written to the chip in PCI target mode, de-compressed with an internal JPEG core, and block inter-leave picture data is output in PCI target mode.

- 4.8 Still Image Compression

- 1 frame image compression stored in frame memory and data output in PCI target or master mode.

- The memory storing range of target picture data can be specified by register setup by B X(Y) BASE and B X(Y) RANGE.

- A command is executed immediately, without synchronizing with VS.

- 4.9 Still Image Output

- One Frame Read-out, data output in PCI Target or Master mode of Frame Memory Storing Picture.

- The memory storing range of target picture data can be specified by register setup by B X(Y) BASE and B X(Y) RANGE.

- A command is executed immediately, without synchronizing with VS.

4.10 Still Image De-Compression

- 1 Frame compressed data input in PCI Target or master mode, de-compress and data store to frame memory.

- The memory storing range of target picture data can be specified by register setup by

B\_X(Y) BASE and B\_X(Y) RANGE.

- A command is executed immediately, without synchronizing with VS.

4.11 Still Image Capture and Compression

- 1 frame still image capture, compression and data output in PCI target or master mode.

- It can perform by combining two micro commands, still picture capture processing of 4.4, and still picture compression processing of 4.8.

4.12 Still image De-compression & Display (only in digital YC mode)

- 1 frame compressed data input in PCI target or master mode and de-compress, store to frame memory

- It can perform by combining two micro commands, still picture de-compression of 4.9, and still picture display of 4.5.

4.13 Continuous Picture Capture & Compression

- Capture and compression every N frame, data output to main memory in PCI master mode

- Frame interval N is set to register, the value is from 0 (every frame) to 31 (every 32 frames)

- When a bottleneck is in a processing flow and processing is not completed within the

specified frame time, the subsequent frame picture for processing is missing.

| FR#1                                 | FR#2                                                                                                | FR#3                                                                                                                                                                             | FR#4                                                                                                                                                                                                                                                                                                                      | FR#5                                                  | FR#6                                                  | FR#7                                                  | FR#8                                                  | FR#9                                                  |                                                       |

|--------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

| cap#1(A)<br>Video $\rightarrow$ FM F | $\begin{array}{c} \text{comp#1} & \text{pro}\\ \hline M \rightarrow PCI \rightarrow MM \end{array}$ | c#1<br>MM → PCI → HD                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                           | cap#5(A)                                              | wait comp<br>done com                                 | wait proc<br>p#5done<br>zza12                         | proc#5<br>10                                          |                                                       |                                                       |

|                                      | cap#2(B)                                                                                            | comp#2                                                                                                                                                                           | proc#2                                                                                                                                                                                                                                                                                                                    | -0                                                    |                                                       | cap#7(B)                                              | comp#7                                                | proc#7<br>0                                           |                                                       |

|                                      |                                                                                                     | cap#3(A)                                                                                                                                                                         | wait<br>comp#3 don                                                                                                                                                                                                                                                                                                        | proc<br>e proc#3<br>1                                 | 0                                                     |                                                       | cap#8                                                 |                                                       |                                                       |

|                                      |                                                                                                     |                                                                                                                                                                                  | cap#4(B)                                                                                                                                                                                                                                                                                                                  | comp#4                                                |                                                       | proc#4                                                |                                                       |                                                       |                                                       |

| Comp : FN                            | $A \rightarrow VRJ \rightarrow MCC -$                                                               | $\rightarrow$ HIC $\rightarrow$ PCIIF $\rightarrow$                                                                                                                              | PCI → MM                                                                                                                                                                                                                                                                                                                  |                                                       |                                                       |                                                       | END in                                                | IRQ                                                   |                                                       |

|                                      | cap#1(A)<br>Video → FM F<br>Note : cap : vic<br>Comp : FN                                           | cap#1(A)     comp#1     pressure       Video $\rightarrow$ FM     FM $\rightarrow$ PCI $\rightarrow$ MM     cap#2(B)       Note : cap : video $\rightarrow$ MCC $\rightarrow$ FM | $\begin{array}{c} cap \#1(A) & comp \#1 \\ \hline comp \#1 \\ \hline comp \#1 \\ \hline comp \#2 \\ \hline cap \#2(B) & comp \#2 \\ \hline cap \#3(A) \\ \hline \\ Note: cap: video \rightarrow MCC \rightarrow FM \\ Comp: FM \rightarrow VRJ \rightarrow MCC \rightarrow HIC \rightarrow PCIIF \rightarrow \end{array}$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

4.14 Continuous Picture Output

- Every N frame capture, frame memory read-out and data output to main memory in PCI master mode

- Frame interval N is set to register, the value is from 0 (every frame) to 31 (every 32 frames)

- When a bottleneck is in a processing flow and processing is not completed within the specified frame time, the subsequent frame picture for processing is missing.

- The picture output format to a PCI bus is pixel sequential and the byte arrangement is as follows

| $\begin{array}{c c} \underline{Video \ Bus} \\ PCL & \underline{Y} \\ Tn & \underline{U} \\ Tn+1 & \underline{Y} \\ \underline{V} \end{array}$ | V         B3           Y         B2           U         B1           Y         B0(LSByte) |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Video Bus                                                                                                                                      | PCI Bus                                                                                   |

| PCL Y                                                                                                                                          | Y B3                                                                                      |

| Tn U                                                                                                                                           | V B2                                                                                      |

| Tn+1 Y                                                                                                                                         | Y B1                                                                                      |

| V                                                                                                                                              | U B0(LSByte)                                                                              |

| rev0.2 99.1.21 | FR#1                   | FR#2                                    | FR#3              | FR#4              | FR#5                  | FR#6                | FR#7              | FR#8         | FR#9    |  |

|----------------|------------------------|-----------------------------------------|-------------------|-------------------|-----------------------|---------------------|-------------------|--------------|---------|--|

| FI Reg#1 0     | cap#1(A)<br>Video → FM | out#1 pro                               | c#10<br>MM→PCI→HD |                   | cap#5(A)              | wait out<br>done ou | wait proc<br>done | proc#5<br>10 |         |  |

| FI Reg#2 0     |                        | cap#2(B)                                | out#2             | proc#2            | 0                     |                     | cap#7(B)          | out#7        | proc#70 |  |

| FI Reg#3 0     |                        |                                         | cap#3(A)          | wait<br>out#3 don | proc<br>e proc#3<br>1 | 0                   |                   | cap#8        |         |  |

| FI Reg#4 0     | N                      |                                         |                   | cap#4(B)          | out#4                 |                     | proc#4            |              |         |  |

|                | Comp : FN              | leo→MCC→FM<br>4→MCC→HIC→P(<br>IM→PCI→HD | СШҒ→РСІ→ММ        |                   |                       |                     |                   | END in       | IRQ     |  |

4.15 Continuous Picture de-compression & Display (only in digital YC mode)

Read-out from main memory in PCI master mode and de-compression, store to frame memory and display. Display changes when a frame memory is updated (every N frames).

Frame interval N is set to register, the value is from 0 (every frame) to 31 (every 32 frames)

When a bottleneck is in a processing flow and processing is not completed within the specified frame time, the subsequent frame picture for processing is missing.

| rev0.2 99.1.21 | FR#1                                | FR#2                          | FR#3          | FR#4       | FR#5                | FR#6              | FR#7           | FR#8       | FR#9         | FR#10     | FR#11       |

|----------------|-------------------------------------|-------------------------------|---------------|------------|---------------------|-------------------|----------------|------------|--------------|-----------|-------------|

| display        | not display                         |                               | disp#1(A)     | disp#2(B)  | disp#2(B)           | disp#3(A)         | disp#4(B)      | disp#4(B)  | disp#5(A)    | disp#6(B) | not display |

| FI Reg#1 0     | proc#1 wai<br>vs<br>01<br>HD→PCI→MM | t<br>1<br><u>1 MM→PCI</u> PFN | FM→video      |            |                     | ait wai<br>cmp vs | t decmp#5<br>1 |            |              |           |             |

| FI Reg#2 0     | рі<br>0                             | roc#2 wait<br>vs<br>1         | decmp#2<br>10 |            | pro                 | c#6 wait<br>decmp |                | wait<br>vs | decmp#6<br>1 |           |             |

| FI Reg#3 0     |                                     | 0                             | proc#3        | wait<br>vs | decmp#3             | 3+                |                |            |              |           |             |

| FI Reg#4 0     |                                     |                               |               | proc#4     | wait wa<br>decmp vs | decmp#4           |                |            |              | IDO       |             |

|                | · ·                                 |                               | HIC→MCC→VRJ   | →FM        |                     |                   |                |            | END in       | IRQ       |             |

4.16 Camera Capture

- If a TAKE\_PICN signal is made active when an internal flag HOST\_USEREQ is 0, the VGA size still image will be captured in the next VS term.

- When the picture captured by camera capture processing is in a frame memory, an internal PIC\_SAVED flag is set.

- A past capture data is overwritten when two or more TAKE\_PICN signal pulse inputs.

- An internal TP\_BUSY flag is set to 1 during camera capture processing execution.

- When a TP\_BUSY flag is 0 and a HOST\_USEREQ flag is 1, a TAKE\_PICN pulse input is disregarded.

4.17 Low Power Mode

- If LOWPOWER register in HIC register domain is set to 1, this chip will set the SDRAM to power down mode, and will suspend the clock inside MCORE.

- When LOWPOWER register is set, negate a MCORE\_RDY signal.

- Setup and release of LOWPOWER register must be performed when HOST\_USEREQ is 1.

Note: Even when HOST\_USEREQ is 0, a setup and release are possible for LOWPOWER register.

However, if LSI is not idle, incorrect operation may be performed after release.

In this case, it is required to input a soft reset command and to initialize a chip.

(This means canceling lowpower mode with a soft reset flag.)

- A setup, release, and a monitor of LOWPOWER register are possible by PCI configuration access. A setup and release of LOWPOWER should be based on the setup and release by LOWPOWER register.

#### 4.18 PCI CLKRUNN signal

- When device status is in D0 (ACTIVE) and a HOST\_USEREQ flag is 1, this chip requires that PCI CLK is 33MHz. When CLKRUNN is negated and change of clock speed is notified, a device asserts 1T term of the CLKRUNN, and requires hold a clock to 33MHz.

Note : It is not concerned with device status in fact, but when a HOST\_USEREQ flag is 1, it is always required that PCI CLK is 33MHz.

4.19 Reset of MCORE block

- Initialization inside MCORE block is performed by the assert of SYSRSTN, or the soft reset flag. Initialization of SDRAM is performed after an end of reset.

8

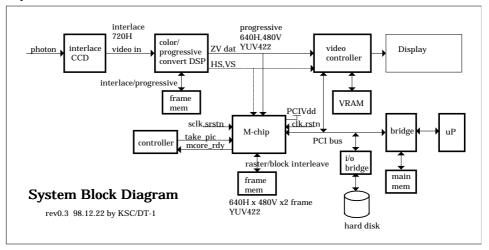

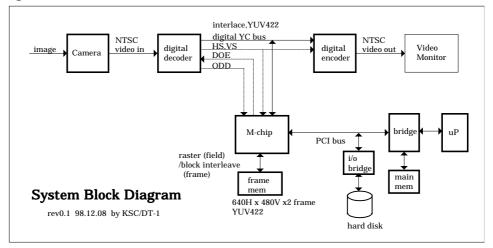

# 4.20 Example of system configuration

\* ZV-port mode :

\* Digital YC mode :

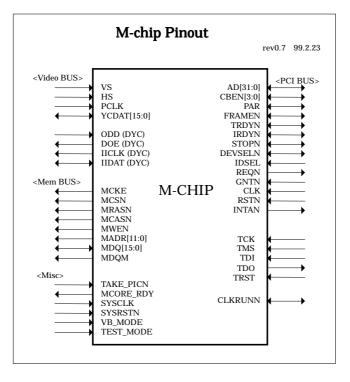

# 5. Logical signal arrangement

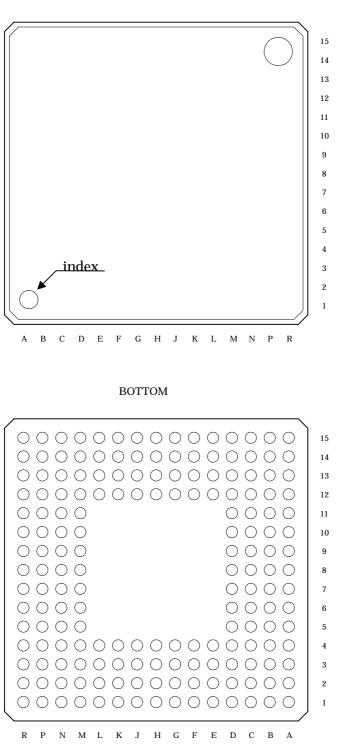

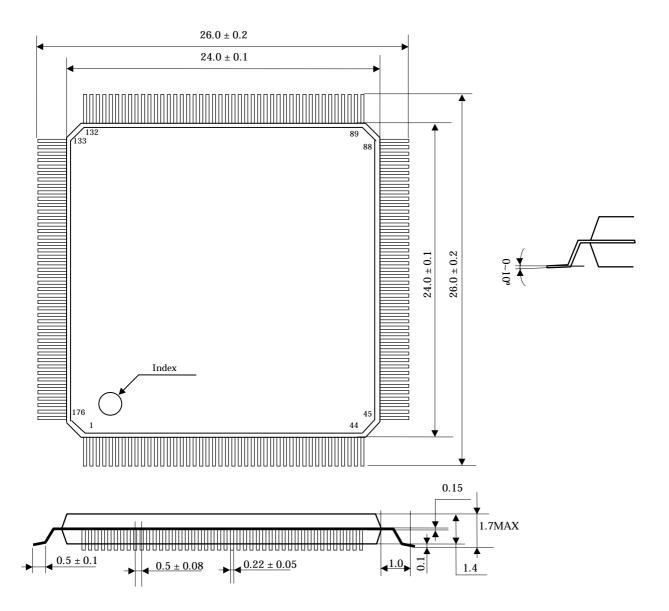

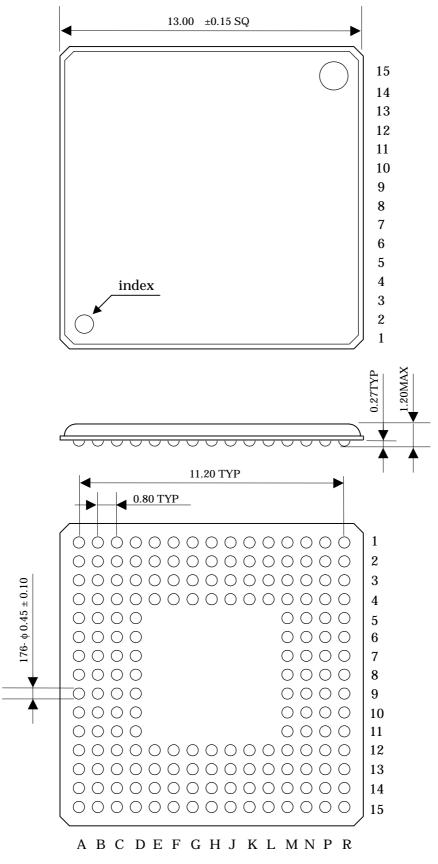

# 6A. Pin arranegement diagram (FBGA176)

The pin arrangement of FBGA176 package is shown below.

TOP VIEW

All right reserved. Company Confidential © 1999 kawasaki Steel Corporation

# 7A. Package pin table (FBGA176)

The pin of FBGA176 package and correspondence of a signal name are shown below.

FBGA176 pin table rev 0.4 99.2.12

| Pin       | I/O        | Signal       | Pin        | I/O        | Signal       | Pin      | I/O        | Signal        | Pin       | I/O        | Signal         |

|-----------|------------|--------------|------------|------------|--------------|----------|------------|---------------|-----------|------------|----------------|

| No.       | 1/0        | name         | No.        | 1/0        | name         | No.      | 1/0        | name          | No.       | 1/0        | name           |

| A1        | I/O        | AD30         | C15        | I/O        | MDAT2        | H12      | I/O        | MDAT11        | N2        | I/O        | AD14           |

| A1<br>A2  | 1/0        | gnd          | D1         | 1/0        | gnd          | H13      | -          | gnd           | N3        | 1/0        | vdd            |

| A3        | I          | GNTN         | D1<br>D2   | I/O        | AD25         | H14      | -          | gnd           | N4        | I/O        | AD10           |

| A4        | 0          | INTAN        | D2<br>D3   | I/O<br>I/O | AD23<br>AD28 | H15      | -          | gnd           | N5        | -          | vdd            |

| A4<br>A5  | I          | TDI          | D3<br>D4   | I/O        | AD28<br>AD29 | J1       | I/O        | AD16          | N6        | I/O        | AD6            |

| лJ        | 1          | (JTAG)       | Di         | 1/0        | AD25         | 51       | 1/0        | ADIO          | 110       | 1/0        | ADU            |

| A6        | Ι          | TRST         | D5         | I/O        | CLKRUNN      | J2       | -          | vdd           | N7        | I/O        | AD4            |

| 110       | 1          | (JTAG)       | 20         | 1/0        | olinioini    | 52       |            | Vuu           |           | 10         |                |

| A7        | Ι          | HS           | D6         | Ι          | TMS          | J3       | -          | gnd           | N8        | I/O        | AD1            |

|           | -          | 110          | 20         | -          | (JTAG)       |          |            | 8             | 110       | 10         |                |

| A8        | -          | vdd          | D7         | Ι          | ODD          | J4       | I/O        | AD17          | N9        | 0          | MDQM           |

| A9        | I/O        | YCDAT12      | D8         | I/O        | YCDAT9       | J12      | I/O        | MDAT14        | N10       | -          | gnd            |

| A10       | I/O        | YCDAT15      | D9         | I/O        | YCDAT11      | J13      | I/O        | MDAT13        | N11       | -          | vdd            |

| A11       | I/O        | YCDAT0       | D10        | -          | vdd          | J14      | I/O        | MDAT12        | N12       | -          | vdd            |

| A12       | I/O        | YCDAT3       | D11        | I/O        | YCDAT2       | J15      | -          | vdd           | N13       | -          | vdd            |

| A13       | -          | vdd          | D12        | I/O        | YCDAT7       | K1       | I/O        | FRAMEN        | N14       | 0          | MADR3          |

| A14       | I/O        | YCDAT6       | D13        | -          | vdd          | K2       | -          | gnd           | N15       | 0          | MADR0          |

| A15       | I/O        | IIDAT        | D14        | -          | gnd          | K3       | I/O        | IRDYN         | P1        | I/O        | CBEN1          |

| B1        | -          | gnd          | D15        | -          | vdd          | K4       | I/O        | CBEN2         | P2        | -          | gnd            |

| B2        | -          | gnd          | E1         | I/O        | CBEN3        | K12      | -          | vdd           | P3        | I/O        | AD11           |

| B3        | I/O        | AD31         | E2         | Ι          | IDSEL        | K13      | -          | gnd           | P4        | -          | gnd            |

| B4        | 0          | REQN         | E3         | I/O        | AD24         | K14      | 0          | MCKE          | P5        | I/O        | CBEN0          |

| B5        | Ι          | CLK          | E4         | -          | vdd          | K15      | I/O        | MDAT15        | P6        | -          | gnd            |

| B6        | -          | gnd          | E12        | I/O        | MDAT4        | L1       | I/O        | TRDYN         | P7        | I/O        | AD2            |

| B7        | Ι          | TCK          | E13        | I/O        | MDAT3        | L2       | I/O        | STOPN         | P8        | -          | gnd            |

| B8        | Ι          | (JTAG)<br>VS | E14        | I/O        | MDAT0        | L3       | -          | gnd           | P9        | Ι          | TEST_MO        |

| B9        | I/O        | YCDAT10      | E15        | I/O        | MDAT6        | L4       | I/O        | DEVSELN       | P10       | Ι          | DE<br>TAKE_PIC |

| D10       | 1/0        | NOD ATIA     |            | T/O        | 1000         | 1.40     |            | ,             | D11       | 0          | N              |

| B10       | I/O        | YCDAT13      | F1         | I/O        | AD22         | L12      | -          | gnd           | P11       | 0          | MADR10         |

| B11       | -          | gnd          | F2         | I/O        | AD21         | L13      | 0          | MWEN          | P12       | -          | gnd            |

| B12       | I/O        | YCDAT4       | F3         | -          | gnd          | L14      | 0          | MRASN         | P13       | 0          | MADR7          |

| B13       | I/O        | YCDAT5       | F4         | I/O        | AD23         | L15      | 0          | MCSN          | P14       | 0          | MADR4          |

| B14       | I<br>I/O   | PCLK         | F12<br>F13 | I/O<br>I/O | MDAT7        | M1       | -          | vdd           | P15<br>R1 | O<br>I/O   | MADR1<br>AD12  |

| B15<br>C1 | I/O<br>I/O | MDAT1        | F13<br>F14 |            | MDAT5        | M2       | -          | gnd<br>vdd    |           | -          |                |

| C1<br>C2  | I/O<br>I/O | AD26<br>AD27 | F14<br>F15 | -          | gnd<br>vdd   | M3<br>M4 | I/O        | AD15          | R2<br>R3  | I/O        | gnd<br>AD9     |

| C2<br>C3  | 1/0        | vdd          | G1         | -<br>I/O   | AD20         | M4<br>M5 | I/O<br>I/O | AD13<br>AD13  | R4        | I/O<br>I/O | AD9<br>AD8     |

| C3<br>C4  | -          |              | G1<br>G2   | I/O<br>I/O |              | M6       | -          |               | R5        | I/O<br>I/O | AD8<br>AD7     |

| C4<br>C5  | I          | vdd<br>RSTN  | G2<br>G3   |            | AD19<br>vdd  | M7       |            | gnd<br>vdd    | R6        | I/O<br>I/O | AD7<br>AD5     |

| C5<br>C6  | 0          | TDO          | G3<br>G4   | -          | gnd          | M8       | -          | gnd           | R7        | I/O<br>I/O | AD3<br>AD3     |

|           | 0          | (JTAG)       |            | -          | _            | 1VIO     | -          | giiu          | 107       | 1/0        | AD3            |

| C7        | 0          | DOE          | G12        | I/O        | MDAT9        | M9       | -          | vdd           | R8        | I/O        | AD0            |

| C8        | I/O        | YCDAT8       | G13        | -          | gnd          | M10      | -          | gnd           | R9        | Ι          | VB_MODE        |

| C9        | -          | gnd          | G14        | I/O        | MDAT8        | M11      | 0          | MCORE_R<br>DY | R10       | Ι          | SYSCLK         |

| C10       | I/O        | YCDAT14      | G15        | I/O        | MDAT10       | M12      | 0          | MADR5         | R11       | Ι          | SYSRSTN        |

| C11       | I/O        | YCDAT1       | H1         | -          | gnd          | M13      | 0          | MADR2         | R12       | 0          | MADR11         |

| C12       | -          | gnd          | H2         | _          | gnd          | M14      | -          | gnd           | R13       | 0          | MADR9          |

| C13       | -          | vdd          | H3         | _          | gnd          | M15      | 0          | MCASN         | R14       | 0          | MADR8          |

| C14       | 0          | IICLK        | H4         | I/O        | AD18         | N1       | I/O        | PAR           | R15       | 0          | MADR6          |

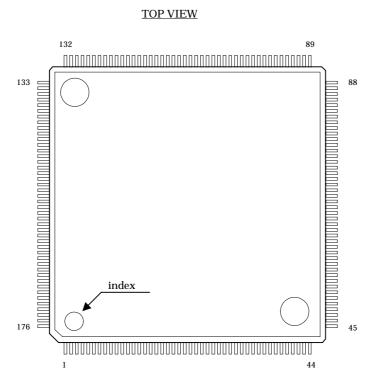

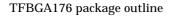

# 6B. Pin arranegement diagram (LQFP176)

The pin arrangement of LQFP176 package is shown below.

$^{\odot}$  1999 kawasaki Steel Corporation ~ All right reserved. Company Confidential

# 7B. Package pin table (LQFP176)

The pin of LQFP176 package and correspondence of a signal name are shown below.

LQFP176 pin table rev 0.3 99.2.12

|       | 7/0        | <i>a</i> , 1 |     | 7/0        | a. 1           |     | 7/0        |                  |     | 7/0        | Gi 1               |

|-------|------------|--------------|-----|------------|----------------|-----|------------|------------------|-----|------------|--------------------|

| Pin   | I/O        | Signal       | Pin | I/O        | Signal         | Pin | I/O        | Signal           | Pin | I/O        | Signal             |

| No.   |            | name         | No. |            | name           | No. |            | name             | No. |            | name               |

|       |            |              |     |            |                |     |            |                  |     |            |                    |

| 1     | -          | vdd          | 45  | -          | vdd            | 89  | -          | vdd              | 133 | -          | vdd                |

| 2     | I/O        | AD29         | 46  | I/O        | AD13           | 90  | 0          | MADR4            | 134 | I/O        | YCDAT7             |

| 3     | I/O        | AD28         | 47  | I/O        | AD12           | 91  | 0          | MADR3            | 135 | I/O        | YCDAT6             |

| 4     | I/O        | AD27         | 48  | I/O        | AD11           | 92  | -          | gnd              | 136 | I/O        | YCDAT5             |

| 5     | -          | gnd          | 49  | -          | gnd            | 93  | 0          | MADR2            | 137 | -          | vdd                |

| 6     | I/O        | AD26         | 50  | I/O        | AD10           | 94  | 0          | MADR1            | 138 | -          | gnd                |

| 7     | I/O        | AD25         | 51  | I/O        | AD9            | 95  | 0          | MADR0            | 139 | I/O        | YCDAT4             |

| 8     | -          | gnd          | 52  | -          | gnd            | 96  | -          | gnd              | 140 | I/O        | YCDAT3             |

| 9     | -          | vdd          | 53  | -          | vdd            | 97  | 0          | MWEN             | 141 | I/O        | YCDAT2             |

| 10    | I/O        | AD24         | 54  | I/O        | AD8            | 98  | 0          | MCASN            | 142 | I/O        | YCDAT1             |

| 11    | I/O        | CBEN3        | 55  | I/O        | CBEN0          | 99  | 0          | MRASN            | 143 | I/O        | YCDAT0             |

| 12    | I          | IDSEL        | 56  | I/O        | AD7            | 100 | -          | vdd              | 144 | -          | gnd                |

| 13    | I/O        | AD23         | 57  | -          | gnd            | 101 | 0          | MCSN             | 145 | -          | vdd                |

| 14    | -          | gnd          | 58  | I/O        | AD6            | 101 | -          | gnd              | 146 | I/O        | YCDAT15            |

| 15    | I/O        | AD22         | 59  | I/O<br>I/O | AD5            | 102 | 0          | MCKE             | 147 | I/O<br>I/O | YCDAT14            |

| 16    | I/O<br>I/O | AD22<br>AD21 | 60  | -          | gnd            | 103 | I/O        | MDAT15           | 147 | I/O<br>I/O | YCDAT13            |

| 17    | -          |              | 61  | -          | vdd            | 104 | I/O<br>I/O | MDAT13<br>MDAT14 | 148 | I/O<br>I/O | YCDAT12            |

| 17    | -          | gnd<br>vdd   | 62  | I/O        | AD4            | 105 | I/O<br>I/O | MDAT14<br>MDAT13 | 149 | I/O<br>I/O | YCDAT12<br>YCDAT11 |

|       | -          | AD20         |     | I/O<br>I/O | AD4<br>AD3     | 100 |            |                  |     |            |                    |

| 19    | I/O        |              | 63  |            |                |     | -          | vdd              | 151 | -          | gnd                |

| 20    | I/O        | AD19         | 64  | I/O        | AD2            | 108 | I/O        | MDAT12           | 152 | -          | vdd                |

| 21    | -          | gnd          | 65  | -          | gnd            | 109 | I/O        | MDAT11           | 153 | I/O        | YCDAT10            |

| 22    | -          | gnd          | 66  | I/O        | AD1            | 110 | -          | gnd              | 154 | I/O        | YCDAT9             |

| 23    | -          | gnd          | 67  | I/O        | AD0            | 111 | -          | gnd              | 155 | I/O        | YCDAT8             |

| 24    | I/O        | AD18         | 68  | -          | gnd            | 112 | -          | gnd              | 156 | I          | HS                 |

| 25    | I/O        | AD17         | 69  | -          | vdd            | 113 | I/O        | MDAT10           | 157 | Ι          | VS                 |

| 26    | I/O        | AD16         | 70  | 0          | MDQM           | 114 | I/O        | MDAT9            | 158 | I          | ODD                |

| 27    | -          | gnd          | 71  | Ι          | VB_MODE        | 115 | -          | gnd              | 159 | 0          | DOE                |

| 28    | -          | vdd          | 72  | Ι          | TEST_MO<br>DE  | 116 | -          | vdd              | 160 | Ι          | TRST (JTAG)        |

| 29    | I/O        | CBEN2        | 73  | -          | gnd            | 117 | I/O        | MDAT8            | 161 | Ι          | TCK<br>(JTAG)      |

| 30    | I/O        | FRAME        | 74  | Ι          | SYSCLK         | 118 | I/O        | MDAT7            | 162 | Ι          | TMS                |

|       |            | Ν            |     |            |                |     |            |                  |     |            | (JTAG)             |

| 31    | I/O        | IRDYN        | 75  | -          | gnd            | 119 | I/O        | MDAT6            | 163 | 0          | TDO                |

|       |            |              |     |            | 0              |     |            |                  |     |            | (JTAG)             |

| 32    | -          | gnd          | 76  | Ι          | SYSRSTN        | 120 | I/O        | MDAT5            | 164 | Ι          | TDI (JTAG)         |

| 33    | I/O        | TRDYN        | 77  | Ι          | TAKE_PIC       | 121 | -          | gnd              | 165 | -          | gnd                |

|       |            |              |     |            | Ň              |     |            | 0                |     |            | 0                  |

| 34    | I/O        | DEVSEL       | 78  | 0          | MCORE_R        | 122 | -          | vdd              | 166 | I/O        | CLKRUNN            |

| ~ -   |            | N            |     | -          | DY             |     |            |                  |     |            |                    |

| 35    | -          | gnd          | 79  | 0          | MADR11         | 123 | I/O        | MDAT4            | 167 | 0          | INTAN              |

| 36    | -          | vdd          | 80  | 0          | MADR10         | 123 | I/O        | MDAT3            | 168 | I          | RSTN               |

| 37    | I/O        | STOPN        | 81  | 0          | MADR9          | 125 | I/O        | MDAT2            | 169 | I          | CLK                |

| 38    | I/O        | PAR          | 82  | 0          | MADR8          | 126 | I/O        | MDAT1            | 170 | I          | GNTN               |

| 39    | I/O        | CBEN1        | 83  | -          | gnd            | 127 | -          | gnd              | 171 | 0          | REQN               |

| 40    | -          | gnd          | 84  | -          | vdd            | 128 | I/O        | MDAT0            | 172 | -          | gnd                |

| 40    | I/O        | AD15         | 85  | 0          | MADR7          | 129 | I/O<br>I/O | IIDAT            | 172 | I/O        | AD31               |

| 41 42 | I/O<br>I/O | AD13<br>AD14 | 86  | 0          | MADR7<br>MADR6 | 130 | 0          | IICLK            | 173 | I/O<br>I/O | AD31<br>AD30       |

| 42    | - 1/0      |              | 87  | 0          | MADR6<br>MADR5 | 130 | I          | PCLK             | 174 | -          |                    |

|       |            | gnd<br>vdd   |     |            | vdd            |     |            |                  |     |            | gnd<br>vdd         |

| 44    | -          | vuu          | 88  | -          | vuu            | 132 | -          | vdd              | 176 | -          | vuu                |

# 8. Signal specification

| No. | Signal name        | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|--------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   |                    | 1/0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| -   | PCI Bus            | 1/0 | DCI address data hus. The sucle which asserted EDAMEN is an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1-1 | AD[31:0] (t/s)     | I/O | PCI address, data bus. The cycle which asserted FRAMEN is an address phase. In a data phase, when it asserts IRDYN and TRDYN simultaneously, data transmission is performed.<br>Endian form is Little Endian form that Most Significant Byte are stored in AD [31:24] (high byte address) and Least Significant Byte in AD [7:0] (low byte address).                                                                                                                                                                                                                                                     |

| 1-2 | CBEN[3:0] (t/s)    | I/O | Bus command, byte enable signal. This signal expresses a<br>command in an address phase, and expresses a byte enable in a<br>data phase. In master operation, it becomes an output and input<br>in an target operation.<br>With this product, data transmission is always performed by<br>DWORD (32b), it always outputs CBEN=0h at the time of<br>master operation, in CBEN=Fh, repeals data transmission at the<br>time of target operation (NULL data phase), and otherwise<br>performs transmission processing as data of DWORD.<br>Byte access by CBEN is supported at the time of a configuration. |

| 1-3 | PAR (t/s)          | I/O | Even Parity flag. PAR is set up so that the sum total of the<br>number of bits 1 of AD [31:0], CBEN [3:0], and PAR may serve as<br>even number.<br>PAR is outputted by 1T delay at the time of AD output, parity is<br>calculated at the time of AD input, and it compares with PAR<br>input value. The status register [15] of Config space is set to 1 at<br>the time of data parity error detection.<br>The status register [15] of Config space is set to 1 at the time of<br>address parity error detection and when the command register<br>[8, 6] is set, a status register [14] is set to 1.     |

| 1-4 | FRAMEN<br>(s/t/s)  | I/O | Cycle frame signal. Outputs at the time of master operation.<br>It is shown that it is among bus transmission start and a cycle.<br>It becomes TS output in master mode and becomes an input in<br>target mode.                                                                                                                                                                                                                                                                                                                                                                                          |

| 1-5 | TRDYN (s/t/s)      | I/O | Target RDY signal. It is shown that the data transmission<br>preparation by the target side is ready. It becomes an input in<br>master mode, and becomes TS output in target mode. It becomes<br>possible only for DEVSELN assert term to output TRDYN.                                                                                                                                                                                                                                                                                                                                                  |

| 1-6 | IRDYN (s/t/s)      | I/O | Initiator RDY signal. It is shown that the data transmission<br>preparation by the master side is ready. It becomes TS output in<br>master mode, and becomes an input in target mode. It becomes<br>possible only for FRAMEN assert term to output IRDYN.                                                                                                                                                                                                                                                                                                                                                |

| 1-7 | STOPN (s/t/s)      | I/O | Target end signal. A stop of a transaction is demanded from a master. It becomes an input in master mode, and becomes TS output in target mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1-8 | DEVSELN<br>(s/t/s) | I/O | Device selection signal. When the target device has recognized access, it asserts.<br>IDSEL and FRAMEN assert at the time of a configuration, and when AD [1:0] is 00b (Type 0 config tran), it asserts.<br>At the time of a usual transaction, the device is mapped to memory space at the time of FRAMEN assert, and an address hits, and when a command can be processed, it asserts.<br>DEVSELN assert timing is Medium (after 2T from FRAMEN assert).                                                                                                                                               |

| No.  | Signal name         | I/O | Function                                                                                                                                                                                                                                                                                                                                                          |

|------|---------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | PCI Bus             |     |                                                                                                                                                                                                                                                                                                                                                                   |

| 1-9  | IDSEL (in)          | Ι   | The device selection signal at the time of a configuration. At the time of FRAMEN assert, when IDESEL=H, AD[1:0] =00b and a command are config read or config write a device asserts DEVSELN and starts configration processing.                                                                                                                                  |

| 1-10 | REQN (t/s)          | 0   | PCI bus use request signal. REQN is asserted to arbitrator to use a bus by the master mode. It is set to TS at the time of RSTN assert.                                                                                                                                                                                                                           |

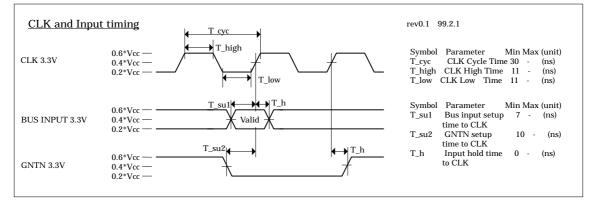

| 1-11 | GNTN (in)           | Ι   | PCI bus use permission signal. GNTN is asserted when<br>arbitrator gives use permission by the master mode at the time<br>of REQN assert. After it asserts GNTN and a master checks that<br>a bus is IDLE (FRAMEN=H and IRDYN=H), it starts a<br>transaction. The value of GNTN is disregarded at the time of<br>RSTN assert.                                     |

| 1-12 | CLK (in)            | Ι   | PCI clock signal. A maximum of 33MHz. When a device is performing internal processing which uses a PCI bus (an internal HOST_USEREQ flag is 1), CLK frequency of 33MHz is required. It is used by PCI interface block. Other internal blocks use SYSCLK signal which is another clock of 33MHz.                                                                   |

| 1-13 | CLKRUNN<br>(in,o/d) | I/O | Clock change / maintenance signal. While a device performs<br>internal processing, the HOST_USEREQ flag is set to 1 by the<br>case where the central resource set CLKRUNN to H and has<br>notified change of the frequency of CLK a device asserts<br>CLKRUNN 1T period, and requires a change failure of it.                                                     |

| 1-14 | RSTN (in)           | Ι   | PCI bus asynchronous reset signal. PCI interface block of a device is reset. A configration register returns to an initial state and REQN, AD, CBEN, and PAR become as TS. Moreover, GNTN in RSTN assert is disregarded. The internal MCORE block of those other than PCI interface is reset by a soft reset command or SYSRSTN signal, and is not reset by RSTN. |

| 1-15 | INTAN (o/d)         | 0   | PCI Interrupt signal. When the interrupt phenomenon of a device occurs, about the phenomenon which has set the interrupt permission flag, INTAN is asserted and interruption processing is required of a system. INTAN signal is negateed when the interrupt flag of PCI IF block is cleared.                                                                     |

The direction and the state of PCI Bus signal are shown below.

In Target access, only when IDSEL, AD, and CBEN are checked and hit at the time of the assert of FRAMEN, DEVSELN is asserted and Target configuration transaction or Target memory transaction is started. Target can interpret and output a signal during the transaction. In Target access, the output of AD and TRDYN is possible at the time of the assert of DEVSELN, and PAR can be output to the term which delayed the assert of DEVSELN 1T, and while FRAMEN or IRDYN is asserting, the output is possible for STOPN. When Master has right to use a bus, it can interpret and output a signal.

|    | Pin name | I/O               | Siganal  | RST | Un-  | Targe | t access           | Mast | er access             |

|----|----------|-------------------|----------|-----|------|-------|--------------------|------|-----------------------|

|    |          | buf               | polarity | Ν   | cnfg | I/O   | condition          | I/O  | condition             |

|    |          |                   |          |     | U    |       | (related signal)   |      | (related signal)      |

| 1  | AD       | bi-dir            |          | in  | in   | Ι     | Addr (FRAMEN asrt) | Ι    | Rdat (TRDYN &         |

|    | [31:0]   | (t/s)             |          |     |      |       | Wdat (IRDYN & hit) |      | DEVSELN)              |

|    |          |                   |          |     |      | 0     | rdat (DEVSELN)     | 0    | Addr (FRAMEN          |

|    |          |                   |          |     |      |       |                    |      | asrt)                 |

|    |          |                   |          |     |      |       |                    |      | Wdat (IRDYN)          |

| 2  | CBEN     | bi-dir            | H(com)   | in  | in   | Ι     | Comm (FRAMEN asrt) | 0    | Comm (FRAMEN          |

|    | [3:0]    | (t/s)             | L(ben)   |     |      |       | Bena (IRDYN)       |      | asrt)                 |

|    |          |                   |          |     |      |       |                    |      | Bena (IRDYN)          |

| 3  | PAR      | bi-dir            |          | in  | in   | Ι     | Addr (FRAMEN +1T)  | Ι    | rddat                 |

|    |          | (t/s)             |          |     |      |       | Wdat (DEVSELN+1T)  |      | (DEVSELN+1T)          |

|    |          |                   |          |     |      | 0     | rddat (DEVSELN+1T) | 0    | Addr (FRAMEN          |

|    |          |                   |          |     |      |       |                    |      | +1T)                  |

|    |          |                   |          |     |      |       |                    |      | Wdat                  |

|    |          | 1 . 1.            |          |     |      |       | 1 4                |      | (DEVSELN+1T)          |

| 4  | FRAME    | bi-dir            | L        | in  | in   | Ι     | hit transaction    | 0    | bus idle (GNTN)       |

| ~  | N        | (s/t/s)           | т        |     |      | 0     |                    | т    | 1.4                   |

| 5  | TRDYN    | bi-dir<br>(s/t/s) | L        | in  | in   | 0     | data tran(DEVSELN) | Ι    | data<br>tran(DEVSELN) |

| 6  | IRDYN    | (s/l/s)<br>bi-dir | L        | in  | in   | Ι     | data tran(DEVSELN) | 0    | tran(DEVSELN)<br>data |

| 0  | IKDIN    | (s/t/s)           | L        | 111 | 111  | 1     | uata tran(DEVSELN) | 0    | tran(DEVSELN)         |

| 7  | STOPN    | bi-dir            | L        | in  | in   | 0     | retry,disconnect   | Ι    | Target tran stop      |

| 1  | STOPN    | (s/t/s)           | L        | 111 | 111  | 0     | (DEVSELN)          | 1    | (FRAMEN or            |

|    |          | (3/1/3)           |          |     |      |       | abort              |      | IRDYN)                |

|    |          |                   |          |     |      |       | (FRAMEN or IRDYN)  |      |                       |

| 8  | DEVSEL   | bi-dir            | L        | in  | in   | 0     | hit transaction    | Ι    | target response       |

| -  | N        | (s/t/s)           | _        |     |      | -     | (FRAMEN or IRDYN)  | _    | (FRAMEN or            |

|    |          | · · /             |          |     |      |       |                    |      | IRDYN)                |

| 9  | IDSEL    | input             | Н        | in  | in   | Ι     | Config access      | NA   |                       |

|    |          | (in)              |          |     |      |       | (FRAMEN assert)    |      |                       |

| 10 | REQN     | 3-st out          | L        | 3-  | out  | NA    |                    | 0    | bus request           |

|    |          | (t/s)             |          | st  |      |       |                    |      | (when ms tran rdy)    |

| 11 | GNTN     | input             | L        | in  | in   | NA    |                    | Ι    | bus granted           |

|    |          | (in)              |          |     |      |       |                    |      | (REQN)                |

| 12 | CLK      | input             | (pos     | in  | in   | Ι     | 33MHz @host_usereq | Ι    | same as target        |

|    |          | (in)              | edge)    |     |      |       |                    |      |                       |

| 13 | CLKRU    | bi-dir            | L        | in  | in   | 0     | Rate change signal | 0    | same as target        |

|    | NN       | (in,o/d)          |          |     |      |       | Keep 33MHz request |      |                       |

|    |          | L                 |          |     |      |       | (D0 & host_usereq) |      |                       |

| 14 | RSTN     | input             | L        | in  | in   | Ι     | PCI IF reset       | Ι    | same as target        |

|    |          | (in)              | -        |     |      | -     | (anytime)          |      |                       |

| 15 | INTAN    | 3-st out          | L        | 3-  | 3-   | 0     | IRQ singal         | 0    | same as target        |

|    |          | (o/d)             |          | st  | st   |       | (anytime)          |      |                       |

| No. | Signal name | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | Video Bus   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

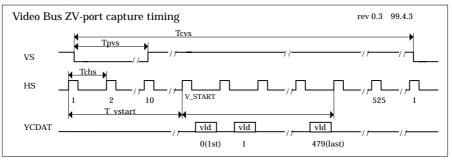

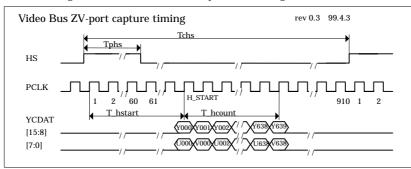

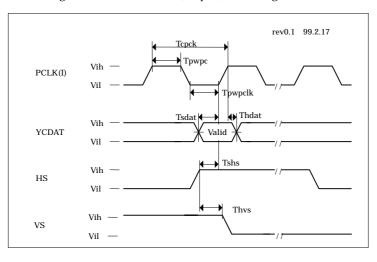

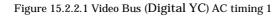

| 2-1 | VS          | I   | Vertical synchronized signal. At the time of ZV-port mode, it is<br>used for discernment of a pause of a frame. In Digital Ycbus<br>mode, it is for discernment of a pause of a field. Specification of<br>the vertical effective range is set as a register via PCI. The assert<br>polarity of VS is programmable. At the time of the ZV-port mode,<br>one VS is asserted in one frame, and the assert timing (falling<br>edge) shall be in the assert (H level) term of HS. |

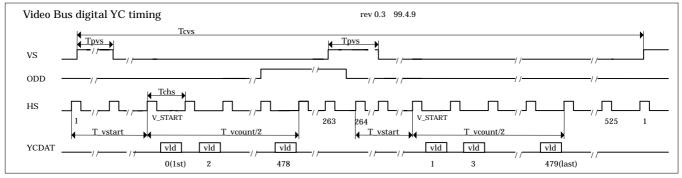

| 2-2 | HS          | Ι   | Horizontal synchronized signal. It is used for discernment of a pause of the horizontal line. Specification of the horizontal effective range is set as a register via PCI. HS is used for the automatic refreshment timing of SDRAM. When HS pulses are not inputted more than 66 $\mu$ secs, It judges that HS is not inputted periodically and continues automatic refreshment of SDRAM using an internal counter. The assert polarity of HS is programmable.              |

| 2-3 | PCLK        | Ι   | Video transmission clock. In ZV-port mode, this clock must be<br>14.318MHz and 12.27MHz in Digital YC bus mode. Each of<br>YCDATs, HSs, and VS is PCLK synchronized signal.                                                                                                                                                                                                                                                                                                   |

| 2-4 | YCDAT[15:0] | I/O | Pixel data. YUV(4:2:2) format. PCLK synchronized signal. In<br>ZV-port progressive mode this bus is input. In Digital YC mode,<br>input at the time of capture and output at the time of DOE active<br>and display. Y data is transmitted to a higher byte, and UV data<br>is transmitted to a low byte. The effective range of YCDAT is<br>programmable. After SYSRSTN assert or soft reset, this bus<br>becomes input mode.                                                 |

| 2-5 | ODD         | I   | The first field indication signal. It is used at the time of Digital YC interlace mode. It asserts during the ODD field. In not using ODD signal, fix to H externally.                                                                                                                                                                                                                                                                                                        |

| 2-6 | DOE         | 0   | YCDAT output indication signal. It is used at the time of Digital YC interlace mode. It asserts during the YCDAT output.                                                                                                                                                                                                                                                                                                                                                      |

| 2-7 | IICLK       | 0   | External video CODEC initial cofiguration signal. It is used if needed.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2-8 | IIDAT       | I/O | External video CODEC initial cofiguration signal. It is used if<br>needed. In TEST_MODE=L (normal operation) and SYSRSTN<br>assert or soft reset command execution, it becomes output mode<br>and in TEST_MODE=H (test mode) becomes I/O mode.                                                                                                                                                                                                                                |

| No. | Signal name | I/O | Function                                                                                             |

|-----|-------------|-----|------------------------------------------------------------------------------------------------------|

| 3   | Mem Bus     |     |                                                                                                      |

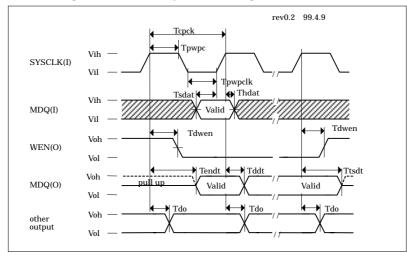

| 3-1 | MCKE        | 0   | Memory clock enable signal.                                                                          |

|     |             |     | Connect to CKE pin of 16Mb SDRAM (524,288 x 16 x 2). Input same clock as SYSCLK to the CLK of SDRAM. |

| 3-2 | MCSN        | 0   | Memory chip select signal.                                                                           |

|     |             |     | Connect to CSN pin of 16Mb SDRAM.                                                                    |

| 3-3 | MRASN       | 0   | Memory ROW address strobe signal.                                                                    |

|     |             |     | Connect to RASN pin of 16Mb SDRAM.                                                                   |

| 3-4 | MCASN       | 0   | Memory COLUMN address strobe signal.                                                                 |

|     |             |     | Connect to CASN pin of 16Mb SDRAM.                                                                   |

| 3-5 | MWEN        | 0   | Memory write enable signal.                                                                          |

|     |             |     | Connect to WEN pin of 16Mb SDRAM.                                                                    |

| 3-6 | MADR[11:0]  | 0   | Memory address signal.                                                                               |

|     |             |     | Connect to the A11-A0 pins of 16Mb SDRAM.                                                            |

| 3-7 | MDQ[15:0]   | I/O | Memory data input/output siganl.                                                                     |

|     |             |     | Connect to the DQ15-DQ0 pin of the 16Mb SDRAM. It becomes                                            |

|     |             |     | output mode after SYSRSTN assert or soft reset command.                                              |

| 3-8 | MDQM        | 0   | Memory data input/output mask signal. Connect with LDQM                                              |

|     |             |     | and UDQM pins of 16Mb SDRAM. It is set to H level at the time                                        |

|     |             |     | after the assert of SYSRSTN signal, soft reset or soft reset of                                      |

|     |             |     | MCC, and it is set to L level after performing the power on                                          |

|     |             |     | sequence of SDRAM. This signal output L level except the above.                                      |

| No. | Signal name   | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | Miscellaneous |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4-1 | VB_MODE       | Ι   | Video Bus operation mode change signal. It becomes ZV_port progressive at the time of VB_MODE=L and Digital YC interlace at the time of H. Must be fixed before a power-on.                                                                                                                                                                                                                                                                                                                     |

| 4-2 | TEST_MODE     | I   | The test mode change signal of a chip. The signal used for LSI test at the time of shipment. It becomes normal operation mode at the time of TEST_MODE=L and becomes test mode at H. Must be fixed before power-on.                                                                                                                                                                                                                                                                             |

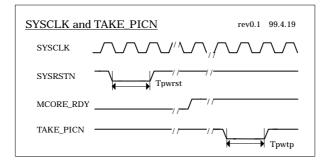

| 4-3 | TAKE_PICN     | I   | The capture control signal in the camera mode. When asserting<br>the MCORE_RDY flag, if this signal is asserted from the<br>exterior, the one frame VGA picture will be captured to SDRAM.<br>In this case, the initial cofiguration from a PCI bus is<br>unnecessary. A TAKE_PICN input is disregarded during the<br>MCORE_RDY negate. As for two or more captures in a<br>MCORE_RDY assert term, only the last picture is saved. When a<br>camera is OFF, TAKE_PICN is externally fixed to H. |

| 4-4 | MCORE_RDY     | 0   | <ul> <li>Indication signal of Capture operation. When capture operation is possible, H level is asserted, and it displays that a capture is possible. When one conditions of the followings are satisfied, it negates.</li> <li>1) During the initialization term of SDRAM by hard reset or soft reset.</li> <li>2) When there is no periodic input of HS signal (at the time of camera-off)</li> <li>3) When LSI is set up in the low power mode</li> </ul>                                    |

| No.  | Signal name   | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|---------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4    | Miscellaneous |     |                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4-5  | ТСК           | Ι   | The terminal only for JTAGs. It is used for a test clock input.<br>JTAG incoming signal is latched at the rising edge of TCK, and<br>JTAG output signal changes at falling edge of TCK.                                                                                                                                                                                                                                              |

| 4-6  | TMS           | Ι   | The terminal only for JTAGs. It is used for test mode selection. It<br>is set to H level by the internal pull-up in the case of un-<br>connecting.                                                                                                                                                                                                                                                                                   |

| 4-7  | TDI           | I   | The terminal only for JTAGs. It is used for a serial test data<br>input. It is set to H level by the internal pull-up in the case of<br>un-connecting.                                                                                                                                                                                                                                                                               |

| 4-8  | TDO           | 0   | The terminal only for JTAGs. It is used for a serial test data output. It is TS output signal.                                                                                                                                                                                                                                                                                                                                       |

| 4-9  | TRST          | Ι   | The terminal only for JTAGs. It is used for test reset input. It is<br>set to H level by the internal pull-up in the case of un-<br>connecting.                                                                                                                                                                                                                                                                                      |

| 4-10 | SYSCLK        | I   | MCORE clock. 33MHz.<br>Connect the same clock as the clock signal connected to MCLK<br>pin of SDRAM. MCORE internal clock is disabled at the time of a<br>low power mode.                                                                                                                                                                                                                                                            |

| 4-11 | SYSRSTN       | I   | MCORE reset signal.<br>Hard reset of the circuits other than PCI interface block is<br>carried out. From PCI side, the inside of MCORE can be<br>initialized like the assert of SYSRSTN by performing a soft reset<br>command. The initial cofiguration of SDRAM is performed after<br>a reset end, and MCORE_RDY is asserted. RSTN of PCI is PCI<br>interface block limitation, and reset of the other circuit is not<br>performed. |

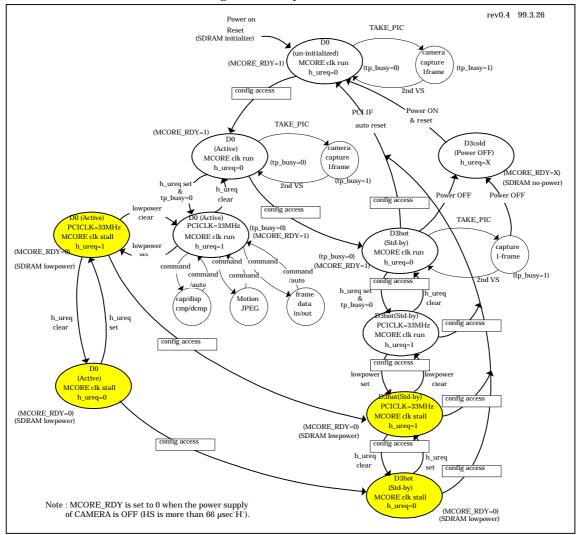

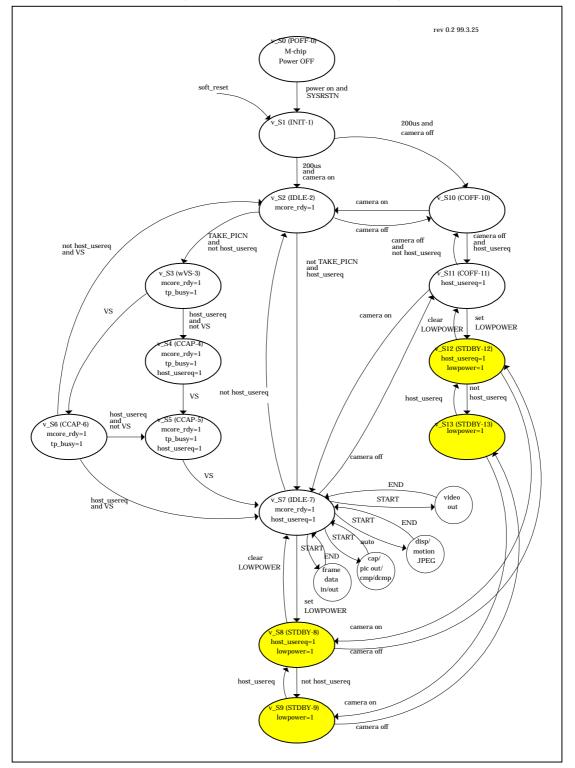

| 9. State | transition | diagram |

|----------|------------|---------|

|          |            |         |

| Device status   | PCI<br>bus status                       | System status                                   | HOST<br>_USEREQ                  | Camera                                | Chip Process                                            |

|-----------------|-----------------------------------------|-------------------------------------------------|----------------------------------|---------------------------------------|---------------------------------------------------------|

| D3cold (OFF)    | B3 (OFF)                                | S5 (OFF)<br>S4<br>(Hybernation)<br>S3 (Suspend) | X                                | OFF                                   | No Power                                                |

| D0 (uninitial)  | B0 (ON)                                 | S0?                                             | 0                                | OFF<br>MCORE_RDY=0                    | Power ON &<br>PCIRST & SYSRST<br>IDLE<br>Camera-Capture |

|                 |                                         |                                                 | 0                                | MCORE_RDY=1<br>OFF                    | IDLE                                                    |

|                 | B0 (ON)<br>PCICLK=33MH                  | S0 (WORKING)                                    |                                  | MCORE_RDY=0<br>ON<br>MCORE_RDY=1      | Camera-Capture                                          |

| D0 (Active)     | z                                       |                                                 | 1                                | OFF<br>MCORE_RDY=0                    | IDLE                                                    |

|                 |                                         |                                                 |                                  | ON<br>Read still image<br>MCORE_RDY=1 | MJPEG Compression<br>Pixel data continuous<br>output    |

|                 |                                         |                                                 | 1<br>LOWPOWER<br>MCORE_RDY<br>=0 | OFF<br>ON                             | Low Power<br>(stop MCORE clk)                           |

|                 | B1 (IDLE)<br>CLK don't care             |                                                 | 0                                | OFF<br>MCORE_RDY=0                    | IDLE                                                    |

|                 |                                         | S1 (IDLE)                                       |                                  | ON<br>MCORE_RDY=1                     | Camera-Capture                                          |